单片机ADC采样

单片机ADC采样

前言:

ADC是单片机中将模拟量转换为数字量的器件,我们称之为魔术转换器,简称ADC。模拟量是指变量在一定时间范围连续变化的量,数字量在时间上是不连续的,离散的。

1 ADC采样原理

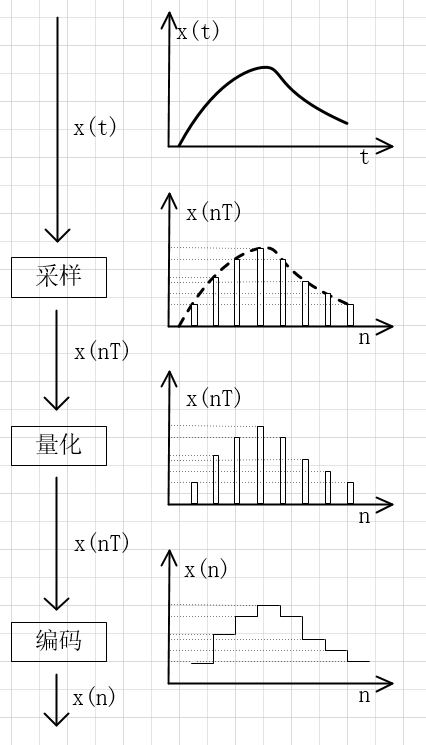

将模拟量转换为数字量的过程一般可分为:采样、保持、量化、编码四个步骤。在实际的转换过程中,这些过程有时是合并进行,比如取样和保持,量化和编码可同时进行。

单片机ADC采样

前言:

ADC是单片机中将模拟量转换为数字量的器件,我们称之为魔术转换器,简称ADC。模拟量是指变量在一定时间范围连续变化的量,数字量在时间上是不连续的,离散的。

1 ADC采样原理

将模拟量转换为数字量的过程一般可分为:采样、保持、量化、编码四个步骤。在实际的转换过程中,这些过程有时是合并进行,比如取样和保持,量化和编码可同时进行。

1.1 采样

将时间连续变化的模拟量转换为时间离散的模拟量。通过控制采样电路开关,使得连续的模拟采样信号被周期性的导通一段时间。这个周期即为ADC的采样周期。

1.2 保持

由于被测模拟信号可能一直处于变化状态,因此为了保证采样的精准性,在量化编码期间应保持被测信号不变,这就是保持的作用。比如对电压的ADC转换,采样电路开关导通后,模拟信号输入进保持电路的电容,开始充电,之后采样断开后电容中的电量被保持,等待量化操作和下一个采样脉冲到来。

1.3 量化

将采样保持后的信号量以某个“最小单位”的整数倍表示,这一过程称为量化。

常见的量化方法有四舍五入法和舍小数法。

1.3.1 四舍五入量化

假设信号量化的最小单位是A,那么把剩余 < A/2** 的部分作为0处理,把剩余 **>= A/2 的部分作为1处理。

1.3.2 舍小数量化

假设信号量化的最小单位是A,那么把剩余 < A 的部分作为0处理。

1.4 编码

把量化的结果用二进制表示的过程称为编码。

2 ADC重要参数

2.1 精度

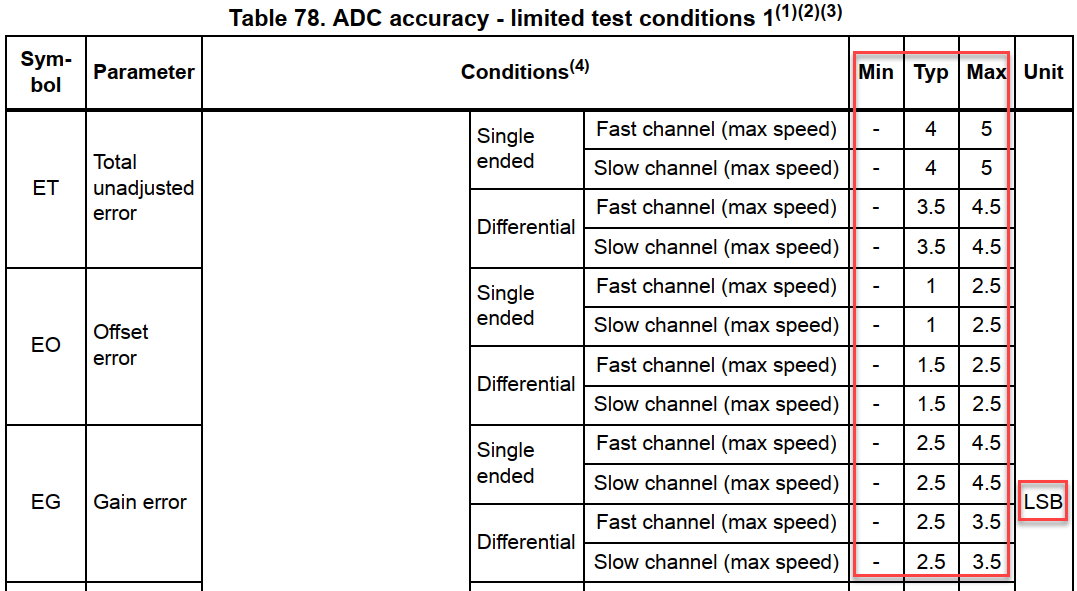

ADC采样精度是衡量ADC采样精准的指标。通常官方的芯片数据手册上都会给出ADC在不同配置和环境下的精度数据。通常我们以偏差多少个LSB(以分辨率衡量精度)来表示ADC精度。比如下图就是ST的手册给出的ADC精度数据。

2.2 分辨率

常见的ADC有8bit、12bit、16bit等,位数反应的是ADC的分辨率。

$$Vref / 2^N$$

比如ADC的参考电压范围是3.3v,那么12bit ADC对应的分辨率为 $3.3v / 2^12 \approx 0.806mv/LSB$ ,因此分辨率约0.806mv,这是12bit ADC在参考电压3.3v所能表示的最小电压刻度,也即1LSB对应的电压值,分辨率也被用来作为衡量ADC精度的单位。

2.3 采样率

指单位时间内采集信号的次数,比如1MHz/s表示ADC一秒采集1M次。采样率越高,相同时间内采集的点数越多,对信号的还原度也就越高,但是需要处理的数据也越多。关于信号采样速率,有个奈奎斯特定律需要遵守。

2.3.1 奈奎斯特定律

奈奎斯特定理又称采样定理,当采样速率大于原始信号中最高频率的2倍以上时,采样后的数字信号可以完整的保留原始信号中的信息,否则采样后信号将会发生混叠导致失真。一般实际运用中保证采样频率是原始信号最高频率的2.56~4倍。

3 常见ADC转换器

常见的ADC转换器有下面几类。

- 转换速度最快的是:并联比较型ADC;

- 转换速度最慢的是:双积分型ADC;

- 转换精度最高的是:双积分型ADC;

- 转换精度最低的是:并联比较型ADC;

- 转换速度和精度均较高的是:逐次比较型ADC;

3.1 逐次逼近型(SAR ADC)

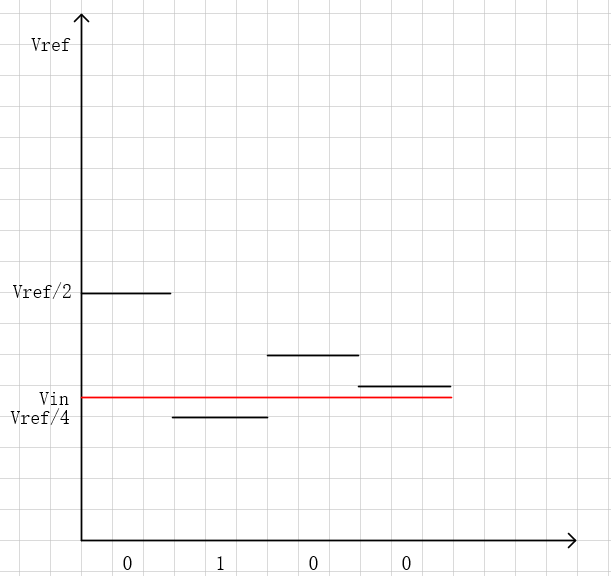

逐次逼近型ADC是目前单片机中应用非常广泛的一类ADC,包含1个比较器、1个DAC、1个逐次逼近寄存器、1个逻辑控制单元。SAR ADC基本原理非常简单,输入电压Vin采样保持电路后电压值被保持住,随后在比较器、DAC、逻辑控制单元作用下按照二进制搜索算法,首先将逐次逼近寄存器最高位置1,对应的DAC输出电压为Vref/2,然后比较器比较DAC的输出和采样保持住的Vin电压,如果 Vin > Vref/2 则比较器输出1,若 Vin < Vref/2 则比较器输出0。逻辑控制单元采集到比较器输出,并将其保存到逐次比较寄存器最高位MSB,随后在逻辑控制单元操控下逐次比较寄存器移动到下一位并先将其置1,逐位比较下去直到比较出所有位即完成编码工作。

以上即为4bit逐位比较ADC的量化编码过程,输出编码结果为0100b。通常N位SAR ADC需要N个比较周期,因此SAR ADC的分辨率越高,完成比较的时间越长。因此高分辨率且高采样率的SAR ADC很少见。可见功耗也与此相关,采样速率越高功耗越高。

特点为当分辨率较低时价格也较低,速率可达MHz,功耗相对也较低。在单片机中运行广泛。

3.2 积分型ADC

积分ADC通过积分器将输入电压转换成数字表示的一种ADC。其原理是把输入的模拟信号转换成与之成正比的时间间隔,然后在这个时间间隔内利用计数器对固定频率的计数脉冲进行技术,计数器的计数值就是AD转换后输出的数字量,它与输入模拟信号成正比。

积分型ADC两次积分的时间都是利用是同一个时钟和计数器,因此D表达式与时钟频率无关,其转换精度只取决于参考电压。因此积分型ADC对交流噪声的干扰有很强的抑制作用,能抑制高频噪声和固定频率的低频干扰。

特点为分辨率高,功耗低,成本低,但转换速率低。在数字电压计等高精度测量仪表中应用广泛。

3.3 并行比较型ADC

并行比较型ADC通过多个高精度电阻将Vref分为多个等级,其中每个等级分别与比较器相连作为其输入,同时比较得出每一位的值,从而实现并行转换的目的。由于是并行转换的,其转换时间只受比较器、触发器、编码电路的延迟时间影响,因此是所有ADC架构设计中转换速度最快的,转换速率可以达到GHz。由于要提高分辨率就需要成倍的增加更多的电路元器件,因此并行比较型ADC难以做到高分辨率,且受到功率和体积的限制。

特点为转换速度快,但分辨率不高,功耗大,成本高。

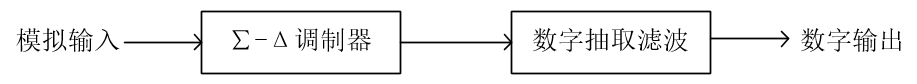

3.4 ∑-Δ型ADC

∑–△型ADC不直接根据抽样数据的每一个样值的大小进行量化编码,而是用前一量值与后一量值的差值即所谓的增量的大小来进行量化编码,某种意义上它是根据波形的包络线进行量化编码的。∑–△型ADC由两部分组成,第一部分为模拟∑–△调制器,第二部分为数字抽取滤波器。△表示增量,∑表示积分或求和。

特点为低速∑-Δ型ADC价格较低,高分辨率能达到24bit,内部利用高倍频过采样技术,实现数字滤波。主要运用于音频和测量。

1.1 采样

将时间连续变化的模拟量转换为时间离散的模拟量。通过控制采样电路开关,使得连续的模拟采样信号被周期性的导通一段时间。这个周期即为ADC的采样周期。

1.2 保持

由于被测模拟信号可能一直处于变化状态,因此为了保证采样的精准性,在量化编码期间应保持被测信号不变,这就是保持的作用。比如对电压的ADC转换,采样电路开关导通后,模拟信号输入进保持电路的电容,开始充电,之后采样断开后电容中的电量被保持,等待量化操作和下一个采样脉冲到来。

1.3 量化

将采样保持后的信号量以某个“最小单位”的整数倍表示,这一过程称为量化。

常见的量化方法有四舍五入法和舍小数法。

1.3.1 四舍五入量化

假设信号量化的最小单位是A,那么把剩余 < A/2** 的部分作为0处理,把剩余 **>= A/2 的部分作为1处理。

1.3.2 舍小数量化

假设信号量化的最小单位是A,那么把剩余 < A 的部分作为0处理。

1.4 编码

把量化的结果用二进制表示的过程称为编码。

2 ADC重要参数

2.1 精度

ADC采样精度是衡量ADC采样精准的指标。通常官方的芯片数据手册上都会给出ADC在不同配置和环境下的精度数据。通常我们以偏差多少个LSB(以分辨率衡量精度)来表示ADC精度。比如下图就是ST的手册给出的ADC精度数据。

单片机ADC采样

前言:

ADC是单片机中将模拟量转换为数字量的器件,我们称之为魔术转换器,简称ADC。模拟量是指变量在一定时间范围连续变化的量,数字量在时间上是不连续的,离散的。

1 ADC采样原理

将模拟量转换为数字量的过程一般可分为:采样、保持、量化、编码四个步骤。在实际的转换过程中,这些过程有时是合并进行,比如取样和保持,量化和编码可同时进行。

1.1 采样

将时间连续变化的模拟量转换为时间离散的模拟量。通过控制采样电路开关,使得连续的模拟采样信号被周期性的导通一段时间。这个周期即为ADC的采样周期。

1.2 保持

由于被测模拟信号可能一直处于变化状态,因此为了保证采样的精准性,在量化编码期间应保持被测信号不变,这就是保持的作用。比如对电压的ADC转换,采样电路开关导通后,模拟信号输入进保持电路的电容,开始充电,之后采样断开后电容中的电量被保持,等待量化操作和下一个采样脉冲到来。

1.3 量化

将采样保持后的信号量以某个“最小单位”的整数倍表示,这一过程称为量化。

常见的量化方法有四舍五入法和舍小数法。

1.3.1 四舍五入量化

假设信号量化的最小单位是A,那么把剩余 < A/2** 的部分作为0处理,把剩余 **>= A/2 的部分作为1处理。

1.3.2 舍小数量化

假设信号量化的最小单位是A,那么把剩余 < A 的部分作为0处理。

1.4 编码

把量化的结果用二进制表示的过程称为编码。

2 ADC重要参数

2.1 精度

ADC采样精度是衡量ADC采样精准的指标。通常官方的芯片数据手册上都会给出ADC在不同配置和环境下的精度数据。通常我们以偏差多少个LSB(以分辨率衡量精度)来表示ADC精度。比如下图就是ST的手册给出的ADC精度数据。

2.2 分辨率

常见的ADC有8bit、12bit、16bit等,位数反应的是ADC的分辨率。

$$Vref / 2^N$$

比如ADC的参考电压范围是3.3v,那么12bit ADC对应的分辨率为 $3.3v / 2^12 \approx 0.806mv/LSB$ ,因此分辨率约0.806mv,这是12bit ADC在参考电压3.3v所能表示的最小电压刻度,也即1LSB对应的电压值,分辨率也被用来作为衡量ADC精度的单位。

2.3 采样率

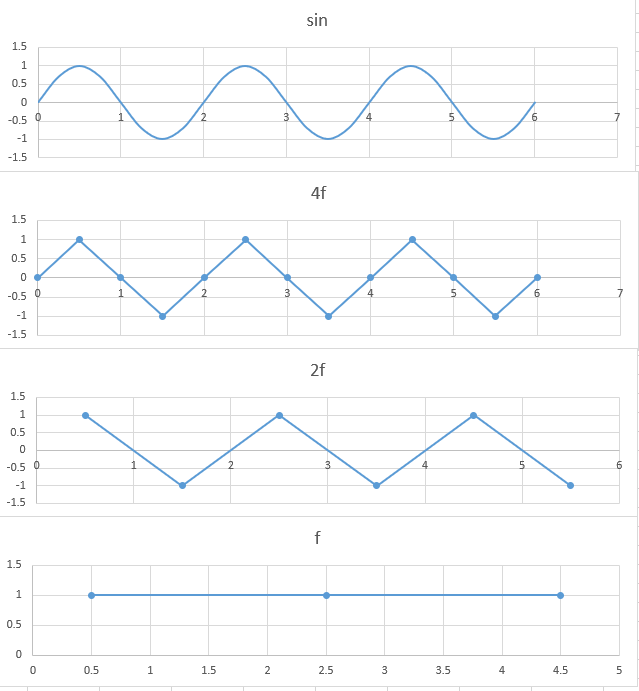

指单位时间内采集信号的次数,比如1MHz/s表示ADC一秒采集1M次。采样率越高,相同时间内采集的点数越多,对信号的还原度也就越高,但是需要处理的数据也越多。关于信号采样速率,有个奈奎斯特定律需要遵守。

2.3.1 奈奎斯特定律

奈奎斯特定理又称采样定理,当采样速率大于原始信号中最高频率的2倍以上时,采样后的数字信号可以完整的保留原始信号中的信息,否则采样后信号将会发生混叠导致失真。一般实际运用中保证采样频率是原始信号最高频率的2.56~4倍。

3 常见ADC转换器

常见的ADC转换器有下面几类。

- 转换速度最快的是:并联比较型ADC;

- 转换速度最慢的是:双积分型ADC;

- 转换精度最高的是:双积分型ADC;

- 转换精度最低的是:并联比较型ADC;

- 转换速度和精度均较高的是:逐次比较型ADC;

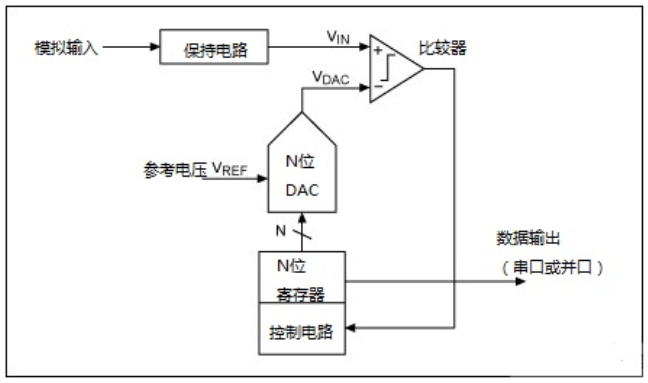

3.1 逐次逼近型(SAR ADC)

逐次逼近型ADC是目前单片机中应用非常广泛的一类ADC,包含1个比较器、1个DAC、1个逐次逼近寄存器、1个逻辑控制单元。SAR ADC基本原理非常简单,输入电压Vin采样保持电路后电压值被保持住,随后在比较器、DAC、逻辑控制单元作用下按照二进制搜索算法,首先将逐次逼近寄存器最高位置1,对应的DAC输出电压为Vref/2,然后比较器比较DAC的输出和采样保持住的Vin电压,如果 Vin > Vref/2 则比较器输出1,若 Vin < Vref/2 则比较器输出0。逻辑控制单元采集到比较器输出,并将其保存到逐次比较寄存器最高位MSB,随后在逻辑控制单元操控下逐次比较寄存器移动到下一位并先将其置1,逐位比较下去直到比较出所有位即完成编码工作。

以上即为4bit逐位比较ADC的量化编码过程,输出编码结果为0100b。通常N位SAR ADC需要N个比较周期,因此SAR ADC的分辨率越高,完成比较的时间越长。因此高分辨率且高采样率的SAR ADC很少见。可见功耗也与此相关,采样速率越高功耗越高。

特点为当分辨率较低时价格也较低,速率可达MHz,功耗相对也较低。在单片机中运行广泛。

3.2 积分型ADC

积分ADC通过积分器将输入电压转换成数字表示的一种ADC。其原理是把输入的模拟信号转换成与之成正比的时间间隔,然后在这个时间间隔内利用计数器对固定频率的计数脉冲进行技术,计数器的计数值就是AD转换后输出的数字量,它与输入模拟信号成正比。

积分型ADC两次积分的时间都是利用是同一个时钟和计数器,因此D表达式与时钟频率无关,其转换精度只取决于参考电压。因此积分型ADC对交流噪声的干扰有很强的抑制作用,能抑制高频噪声和固定频率的低频干扰。

特点为分辨率高,功耗低,成本低,但转换速率低。在数字电压计等高精度测量仪表中应用广泛。

3.3 并行比较型ADC

并行比较型ADC通过多个高精度电阻将Vref分为多个等级,其中每个等级分别与比较器相连作为其输入,同时比较得出每一位的值,从而实现并行转换的目的。由于是并行转换的,其转换时间只受比较器、触发器、编码电路的延迟时间影响,因此是所有ADC架构设计中转换速度最快的,转换速率可以达到GHz。由于要提高分辨率就需要成倍的增加更多的电路元器件,因此并行比较型ADC难以做到高分辨率,且受到功率和体积的限制。

特点为转换速度快,但分辨率不高,功耗大,成本高。

3.4 ∑-Δ型ADC

∑–△型ADC不直接根据抽样数据的每一个样值的大小进行量化编码,而是用前一量值与后一量值的差值即所谓的增量的大小来进行量化编码,某种意义上它是根据波形的包络线进行量化编码的。∑–△型ADC由两部分组成,第一部分为模拟∑–△调制器,第二部分为数字抽取滤波器。△表示增量,∑表示积分或求和。

特点为低速∑-Δ型ADC价格较低,高分辨率能达到24bit,内部利用高倍频过采样技术,实现数字滤波。主要运用于音频和测量。

2.2 分辨率

常见的ADC有8bit、12bit、16bit等,位数反应的是ADC的分辨率。

$$Vref / 2^N$$

比如ADC的参考电压范围是3.3v,那么12bit ADC对应的分辨率为 $3.3v / 2^12 \approx 0.806mv/LSB$ ,因此分辨率约0.806mv,这是12bit ADC在参考电压3.3v所能表示的最小电压刻度,也即1LSB对应的电压值,分辨率也被用来作为衡量ADC精度的单位。

2.3 采样率

指单位时间内采集信号的次数,比如1MHz/s表示ADC一秒采集1M次。采样率越高,相同时间内采集的点数越多,对信号的还原度也就越高,但是需要处理的数据也越多。关于信号采样速率,有个奈奎斯特定律需要遵守。

2.3.1 奈奎斯特定律

奈奎斯特定理又称采样定理,当采样速率大于原始信号中最高频率的2倍以上时,采样后的数字信号可以完整的保留原始信号中的信息,否则采样后信号将会发生混叠导致失真。一般实际运用中保证采样频率是原始信号最高频率的2.56~4倍。

单片机ADC采样

前言:

ADC是单片机中将模拟量转换为数字量的器件,我们称之为魔术转换器,简称ADC。模拟量是指变量在一定时间范围连续变化的量,数字量在时间上是不连续的,离散的。

1 ADC采样原理

将模拟量转换为数字量的过程一般可分为:采样、保持、量化、编码四个步骤。在实际的转换过程中,这些过程有时是合并进行,比如取样和保持,量化和编码可同时进行。

1.1 采样

将时间连续变化的模拟量转换为时间离散的模拟量。通过控制采样电路开关,使得连续的模拟采样信号被周期性的导通一段时间。这个周期即为ADC的采样周期。

1.2 保持

由于被测模拟信号可能一直处于变化状态,因此为了保证采样的精准性,在量化编码期间应保持被测信号不变,这就是保持的作用。比如对电压的ADC转换,采样电路开关导通后,模拟信号输入进保持电路的电容,开始充电,之后采样断开后电容中的电量被保持,等待量化操作和下一个采样脉冲到来。

1.3 量化

将采样保持后的信号量以某个“最小单位”的整数倍表示,这一过程称为量化。

常见的量化方法有四舍五入法和舍小数法。

1.3.1 四舍五入量化

假设信号量化的最小单位是A,那么把剩余 < A/2** 的部分作为0处理,把剩余 **>= A/2 的部分作为1处理。

1.3.2 舍小数量化

假设信号量化的最小单位是A,那么把剩余 < A 的部分作为0处理。

1.4 编码

把量化的结果用二进制表示的过程称为编码。

2 ADC重要参数

2.1 精度

ADC采样精度是衡量ADC采样精准的指标。通常官方的芯片数据手册上都会给出ADC在不同配置和环境下的精度数据。通常我们以偏差多少个LSB(以分辨率衡量精度)来表示ADC精度。比如下图就是ST的手册给出的ADC精度数据。

2.2 分辨率

常见的ADC有8bit、12bit、16bit等,位数反应的是ADC的分辨率。

$$Vref / 2^N$$

比如ADC的参考电压范围是3.3v,那么12bit ADC对应的分辨率为 $3.3v / 2^12 \approx 0.806mv/LSB$ ,因此分辨率约0.806mv,这是12bit ADC在参考电压3.3v所能表示的最小电压刻度,也即1LSB对应的电压值,分辨率也被用来作为衡量ADC精度的单位。

2.3 采样率

指单位时间内采集信号的次数,比如1MHz/s表示ADC一秒采集1M次。采样率越高,相同时间内采集的点数越多,对信号的还原度也就越高,但是需要处理的数据也越多。关于信号采样速率,有个奈奎斯特定律需要遵守。

2.3.1 奈奎斯特定律

奈奎斯特定理又称采样定理,当采样速率大于原始信号中最高频率的2倍以上时,采样后的数字信号可以完整的保留原始信号中的信息,否则采样后信号将会发生混叠导致失真。一般实际运用中保证采样频率是原始信号最高频率的2.56~4倍。

3 常见ADC转换器

常见的ADC转换器有下面几类。

- 转换速度最快的是:并联比较型ADC;

- 转换速度最慢的是:双积分型ADC;

- 转换精度最高的是:双积分型ADC;

- 转换精度最低的是:并联比较型ADC;

- 转换速度和精度均较高的是:逐次比较型ADC;

3.1 逐次逼近型(SAR ADC)

逐次逼近型ADC是目前单片机中应用非常广泛的一类ADC,包含1个比较器、1个DAC、1个逐次逼近寄存器、1个逻辑控制单元。SAR ADC基本原理非常简单,输入电压Vin采样保持电路后电压值被保持住,随后在比较器、DAC、逻辑控制单元作用下按照二进制搜索算法,首先将逐次逼近寄存器最高位置1,对应的DAC输出电压为Vref/2,然后比较器比较DAC的输出和采样保持住的Vin电压,如果 Vin > Vref/2 则比较器输出1,若 Vin < Vref/2 则比较器输出0。逻辑控制单元采集到比较器输出,并将其保存到逐次比较寄存器最高位MSB,随后在逻辑控制单元操控下逐次比较寄存器移动到下一位并先将其置1,逐位比较下去直到比较出所有位即完成编码工作。

以上即为4bit逐位比较ADC的量化编码过程,输出编码结果为0100b。通常N位SAR ADC需要N个比较周期,因此SAR ADC的分辨率越高,完成比较的时间越长。因此高分辨率且高采样率的SAR ADC很少见。可见功耗也与此相关,采样速率越高功耗越高。

特点为当分辨率较低时价格也较低,速率可达MHz,功耗相对也较低。在单片机中运行广泛。

3.2 积分型ADC

积分ADC通过积分器将输入电压转换成数字表示的一种ADC。其原理是把输入的模拟信号转换成与之成正比的时间间隔,然后在这个时间间隔内利用计数器对固定频率的计数脉冲进行技术,计数器的计数值就是AD转换后输出的数字量,它与输入模拟信号成正比。

积分型ADC两次积分的时间都是利用是同一个时钟和计数器,因此D表达式与时钟频率无关,其转换精度只取决于参考电压。因此积分型ADC对交流噪声的干扰有很强的抑制作用,能抑制高频噪声和固定频率的低频干扰。

特点为分辨率高,功耗低,成本低,但转换速率低。在数字电压计等高精度测量仪表中应用广泛。

3.3 并行比较型ADC

并行比较型ADC通过多个高精度电阻将Vref分为多个等级,其中每个等级分别与比较器相连作为其输入,同时比较得出每一位的值,从而实现并行转换的目的。由于是并行转换的,其转换时间只受比较器、触发器、编码电路的延迟时间影响,因此是所有ADC架构设计中转换速度最快的,转换速率可以达到GHz。由于要提高分辨率就需要成倍的增加更多的电路元器件,因此并行比较型ADC难以做到高分辨率,且受到功率和体积的限制。

特点为转换速度快,但分辨率不高,功耗大,成本高。

3.4 ∑-Δ型ADC

∑–△型ADC不直接根据抽样数据的每一个样值的大小进行量化编码,而是用前一量值与后一量值的差值即所谓的增量的大小来进行量化编码,某种意义上它是根据波形的包络线进行量化编码的。∑–△型ADC由两部分组成,第一部分为模拟∑–△调制器,第二部分为数字抽取滤波器。△表示增量,∑表示积分或求和。

特点为低速∑-Δ型ADC价格较低,高分辨率能达到24bit,内部利用高倍频过采样技术,实现数字滤波。主要运用于音频和测量。

3 常见ADC转换器

常见的ADC转换器有下面几类。

- 转换速度最快的是:并联比较型ADC;

- 转换速度最慢的是:双积分型ADC;

- 转换精度最高的是:双积分型ADC;

- 转换精度最低的是:并联比较型ADC;

- 转换速度和精度均较高的是:逐次比较型ADC;

3.1 逐次逼近型(SAR ADC)

逐次逼近型ADC是目前单片机中应用非常广泛的一类ADC,包含1个比较器、1个DAC、1个逐次逼近寄存器、1个逻辑控制单元。SAR ADC基本原理非常简单,输入电压Vin采样保持电路后电压值被保持住,随后在比较器、DAC、逻辑控制单元作用下按照二进制搜索算法,首先将逐次逼近寄存器最高位置1,对应的DAC输出电压为Vref/2,然后比较器比较DAC的输出和采样保持住的Vin电压,如果 Vin > Vref/2 则比较器输出1,若 Vin < Vref/2 则比较器输出0。逻辑控制单元采集到比较器输出,并将其保存到逐次比较寄存器最高位MSB,随后在逻辑控制单元操控下逐次比较寄存器移动到下一位并先将其置1,逐位比较下去直到比较出所有位即完成编码工作。

单片机ADC采样

前言:

ADC是单片机中将模拟量转换为数字量的器件,我们称之为魔术转换器,简称ADC。模拟量是指变量在一定时间范围连续变化的量,数字量在时间上是不连续的,离散的。

1 ADC采样原理

将模拟量转换为数字量的过程一般可分为:采样、保持、量化、编码四个步骤。在实际的转换过程中,这些过程有时是合并进行,比如取样和保持,量化和编码可同时进行。

1.1 采样

将时间连续变化的模拟量转换为时间离散的模拟量。通过控制采样电路开关,使得连续的模拟采样信号被周期性的导通一段时间。这个周期即为ADC的采样周期。

1.2 保持

由于被测模拟信号可能一直处于变化状态,因此为了保证采样的精准性,在量化编码期间应保持被测信号不变,这就是保持的作用。比如对电压的ADC转换,采样电路开关导通后,模拟信号输入进保持电路的电容,开始充电,之后采样断开后电容中的电量被保持,等待量化操作和下一个采样脉冲到来。

1.3 量化

将采样保持后的信号量以某个“最小单位”的整数倍表示,这一过程称为量化。

常见的量化方法有四舍五入法和舍小数法。

1.3.1 四舍五入量化

假设信号量化的最小单位是A,那么把剩余 < A/2** 的部分作为0处理,把剩余 **>= A/2 的部分作为1处理。

1.3.2 舍小数量化

假设信号量化的最小单位是A,那么把剩余 < A 的部分作为0处理。

1.4 编码

把量化的结果用二进制表示的过程称为编码。

2 ADC重要参数

2.1 精度

ADC采样精度是衡量ADC采样精准的指标。通常官方的芯片数据手册上都会给出ADC在不同配置和环境下的精度数据。通常我们以偏差多少个LSB(以分辨率衡量精度)来表示ADC精度。比如下图就是ST的手册给出的ADC精度数据。

2.2 分辨率

常见的ADC有8bit、12bit、16bit等,位数反应的是ADC的分辨率。

$$Vref / 2^N$$

比如ADC的参考电压范围是3.3v,那么12bit ADC对应的分辨率为 $3.3v / 2^12 \approx 0.806mv/LSB$ ,因此分辨率约0.806mv,这是12bit ADC在参考电压3.3v所能表示的最小电压刻度,也即1LSB对应的电压值,分辨率也被用来作为衡量ADC精度的单位。

2.3 采样率

指单位时间内采集信号的次数,比如1MHz/s表示ADC一秒采集1M次。采样率越高,相同时间内采集的点数越多,对信号的还原度也就越高,但是需要处理的数据也越多。关于信号采样速率,有个奈奎斯特定律需要遵守。

2.3.1 奈奎斯特定律

奈奎斯特定理又称采样定理,当采样速率大于原始信号中最高频率的2倍以上时,采样后的数字信号可以完整的保留原始信号中的信息,否则采样后信号将会发生混叠导致失真。一般实际运用中保证采样频率是原始信号最高频率的2.56~4倍。

3 常见ADC转换器

常见的ADC转换器有下面几类。

- 转换速度最快的是:并联比较型ADC;

- 转换速度最慢的是:双积分型ADC;

- 转换精度最高的是:双积分型ADC;

- 转换精度最低的是:并联比较型ADC;

- 转换速度和精度均较高的是:逐次比较型ADC;

3.1 逐次逼近型(SAR ADC)

逐次逼近型ADC是目前单片机中应用非常广泛的一类ADC,包含1个比较器、1个DAC、1个逐次逼近寄存器、1个逻辑控制单元。SAR ADC基本原理非常简单,输入电压Vin采样保持电路后电压值被保持住,随后在比较器、DAC、逻辑控制单元作用下按照二进制搜索算法,首先将逐次逼近寄存器最高位置1,对应的DAC输出电压为Vref/2,然后比较器比较DAC的输出和采样保持住的Vin电压,如果 Vin > Vref/2 则比较器输出1,若 Vin < Vref/2 则比较器输出0。逻辑控制单元采集到比较器输出,并将其保存到逐次比较寄存器最高位MSB,随后在逻辑控制单元操控下逐次比较寄存器移动到下一位并先将其置1,逐位比较下去直到比较出所有位即完成编码工作。

以上即为4bit逐位比较ADC的量化编码过程,输出编码结果为0100b。通常N位SAR ADC需要N个比较周期,因此SAR ADC的分辨率越高,完成比较的时间越长。因此高分辨率且高采样率的SAR ADC很少见。可见功耗也与此相关,采样速率越高功耗越高。

特点为当分辨率较低时价格也较低,速率可达MHz,功耗相对也较低。在单片机中运行广泛。

3.2 积分型ADC

积分ADC通过积分器将输入电压转换成数字表示的一种ADC。其原理是把输入的模拟信号转换成与之成正比的时间间隔,然后在这个时间间隔内利用计数器对固定频率的计数脉冲进行技术,计数器的计数值就是AD转换后输出的数字量,它与输入模拟信号成正比。

积分型ADC两次积分的时间都是利用是同一个时钟和计数器,因此D表达式与时钟频率无关,其转换精度只取决于参考电压。因此积分型ADC对交流噪声的干扰有很强的抑制作用,能抑制高频噪声和固定频率的低频干扰。

特点为分辨率高,功耗低,成本低,但转换速率低。在数字电压计等高精度测量仪表中应用广泛。

3.3 并行比较型ADC

并行比较型ADC通过多个高精度电阻将Vref分为多个等级,其中每个等级分别与比较器相连作为其输入,同时比较得出每一位的值,从而实现并行转换的目的。由于是并行转换的,其转换时间只受比较器、触发器、编码电路的延迟时间影响,因此是所有ADC架构设计中转换速度最快的,转换速率可以达到GHz。由于要提高分辨率就需要成倍的增加更多的电路元器件,因此并行比较型ADC难以做到高分辨率,且受到功率和体积的限制。

特点为转换速度快,但分辨率不高,功耗大,成本高。

3.4 ∑-Δ型ADC

∑–△型ADC不直接根据抽样数据的每一个样值的大小进行量化编码,而是用前一量值与后一量值的差值即所谓的增量的大小来进行量化编码,某种意义上它是根据波形的包络线进行量化编码的。∑–△型ADC由两部分组成,第一部分为模拟∑–△调制器,第二部分为数字抽取滤波器。△表示增量,∑表示积分或求和。

特点为低速∑-Δ型ADC价格较低,高分辨率能达到24bit,内部利用高倍频过采样技术,实现数字滤波。主要运用于音频和测量。

单片机ADC采样

前言:

ADC是单片机中将模拟量转换为数字量的器件,我们称之为魔术转换器,简称ADC。模拟量是指变量在一定时间范围连续变化的量,数字量在时间上是不连续的,离散的。

1 ADC采样原理

将模拟量转换为数字量的过程一般可分为:采样、保持、量化、编码四个步骤。在实际的转换过程中,这些过程有时是合并进行,比如取样和保持,量化和编码可同时进行。

1.1 采样

将时间连续变化的模拟量转换为时间离散的模拟量。通过控制采样电路开关,使得连续的模拟采样信号被周期性的导通一段时间。这个周期即为ADC的采样周期。

1.2 保持

由于被测模拟信号可能一直处于变化状态,因此为了保证采样的精准性,在量化编码期间应保持被测信号不变,这就是保持的作用。比如对电压的ADC转换,采样电路开关导通后,模拟信号输入进保持电路的电容,开始充电,之后采样断开后电容中的电量被保持,等待量化操作和下一个采样脉冲到来。

1.3 量化

将采样保持后的信号量以某个“最小单位”的整数倍表示,这一过程称为量化。

常见的量化方法有四舍五入法和舍小数法。

1.3.1 四舍五入量化

假设信号量化的最小单位是A,那么把剩余 < A/2** 的部分作为0处理,把剩余 **>= A/2 的部分作为1处理。

1.3.2 舍小数量化

假设信号量化的最小单位是A,那么把剩余 < A 的部分作为0处理。

1.4 编码

把量化的结果用二进制表示的过程称为编码。

2 ADC重要参数

2.1 精度

ADC采样精度是衡量ADC采样精准的指标。通常官方的芯片数据手册上都会给出ADC在不同配置和环境下的精度数据。通常我们以偏差多少个LSB(以分辨率衡量精度)来表示ADC精度。比如下图就是ST的手册给出的ADC精度数据。

2.2 分辨率

常见的ADC有8bit、12bit、16bit等,位数反应的是ADC的分辨率。

$$Vref / 2^N$$

比如ADC的参考电压范围是3.3v,那么12bit ADC对应的分辨率为 $3.3v / 2^12 \approx 0.806mv/LSB$ ,因此分辨率约0.806mv,这是12bit ADC在参考电压3.3v所能表示的最小电压刻度,也即1LSB对应的电压值,分辨率也被用来作为衡量ADC精度的单位。

2.3 采样率

指单位时间内采集信号的次数,比如1MHz/s表示ADC一秒采集1M次。采样率越高,相同时间内采集的点数越多,对信号的还原度也就越高,但是需要处理的数据也越多。关于信号采样速率,有个奈奎斯特定律需要遵守。

2.3.1 奈奎斯特定律

奈奎斯特定理又称采样定理,当采样速率大于原始信号中最高频率的2倍以上时,采样后的数字信号可以完整的保留原始信号中的信息,否则采样后信号将会发生混叠导致失真。一般实际运用中保证采样频率是原始信号最高频率的2.56~4倍。

3 常见ADC转换器

常见的ADC转换器有下面几类。

- 转换速度最快的是:并联比较型ADC;

- 转换速度最慢的是:双积分型ADC;

- 转换精度最高的是:双积分型ADC;

- 转换精度最低的是:并联比较型ADC;

- 转换速度和精度均较高的是:逐次比较型ADC;

3.1 逐次逼近型(SAR ADC)

逐次逼近型ADC是目前单片机中应用非常广泛的一类ADC,包含1个比较器、1个DAC、1个逐次逼近寄存器、1个逻辑控制单元。SAR ADC基本原理非常简单,输入电压Vin采样保持电路后电压值被保持住,随后在比较器、DAC、逻辑控制单元作用下按照二进制搜索算法,首先将逐次逼近寄存器最高位置1,对应的DAC输出电压为Vref/2,然后比较器比较DAC的输出和采样保持住的Vin电压,如果 Vin > Vref/2 则比较器输出1,若 Vin < Vref/2 则比较器输出0。逻辑控制单元采集到比较器输出,并将其保存到逐次比较寄存器最高位MSB,随后在逻辑控制单元操控下逐次比较寄存器移动到下一位并先将其置1,逐位比较下去直到比较出所有位即完成编码工作。

以上即为4bit逐位比较ADC的量化编码过程,输出编码结果为0100b。通常N位SAR ADC需要N个比较周期,因此SAR ADC的分辨率越高,完成比较的时间越长。因此高分辨率且高采样率的SAR ADC很少见。可见功耗也与此相关,采样速率越高功耗越高。

特点为当分辨率较低时价格也较低,速率可达MHz,功耗相对也较低。在单片机中运行广泛。

3.2 积分型ADC

积分ADC通过积分器将输入电压转换成数字表示的一种ADC。其原理是把输入的模拟信号转换成与之成正比的时间间隔,然后在这个时间间隔内利用计数器对固定频率的计数脉冲进行技术,计数器的计数值就是AD转换后输出的数字量,它与输入模拟信号成正比。

积分型ADC两次积分的时间都是利用是同一个时钟和计数器,因此D表达式与时钟频率无关,其转换精度只取决于参考电压。因此积分型ADC对交流噪声的干扰有很强的抑制作用,能抑制高频噪声和固定频率的低频干扰。

特点为分辨率高,功耗低,成本低,但转换速率低。在数字电压计等高精度测量仪表中应用广泛。

3.3 并行比较型ADC

并行比较型ADC通过多个高精度电阻将Vref分为多个等级,其中每个等级分别与比较器相连作为其输入,同时比较得出每一位的值,从而实现并行转换的目的。由于是并行转换的,其转换时间只受比较器、触发器、编码电路的延迟时间影响,因此是所有ADC架构设计中转换速度最快的,转换速率可以达到GHz。由于要提高分辨率就需要成倍的增加更多的电路元器件,因此并行比较型ADC难以做到高分辨率,且受到功率和体积的限制。

特点为转换速度快,但分辨率不高,功耗大,成本高。

3.4 ∑-Δ型ADC

∑–△型ADC不直接根据抽样数据的每一个样值的大小进行量化编码,而是用前一量值与后一量值的差值即所谓的增量的大小来进行量化编码,某种意义上它是根据波形的包络线进行量化编码的。∑–△型ADC由两部分组成,第一部分为模拟∑–△调制器,第二部分为数字抽取滤波器。△表示增量,∑表示积分或求和。

特点为低速∑-Δ型ADC价格较低,高分辨率能达到24bit,内部利用高倍频过采样技术,实现数字滤波。主要运用于音频和测量。

以上即为4bit逐位比较ADC的量化编码过程,输出编码结果为0100b。通常N位SAR ADC需要N个比较周期,因此SAR ADC的分辨率越高,完成比较的时间越长。因此高分辨率且高采样率的SAR ADC很少见。可见功耗也与此相关,采样速率越高功耗越高。

特点为当分辨率较低时价格也较低,速率可达MHz,功耗相对也较低。在单片机中运行广泛。

3.2 积分型ADC

积分ADC通过积分器将输入电压转换成数字表示的一种ADC。其原理是把输入的模拟信号转换成与之成正比的时间间隔,然后在这个时间间隔内利用计数器对固定频率的计数脉冲进行技术,计数器的计数值就是AD转换后输出的数字量,它与输入模拟信号成正比。

积分型ADC两次积分的时间都是利用是同一个时钟和计数器,因此D表达式与时钟频率无关,其转换精度只取决于参考电压。因此积分型ADC对交流噪声的干扰有很强的抑制作用,能抑制高频噪声和固定频率的低频干扰。

特点为分辨率高,功耗低,成本低,但转换速率低。在数字电压计等高精度测量仪表中应用广泛。

3.3 并行比较型ADC

并行比较型ADC通过多个高精度电阻将Vref分为多个等级,其中每个等级分别与比较器相连作为其输入,同时比较得出每一位的值,从而实现并行转换的目的。由于是并行转换的,其转换时间只受比较器、触发器、编码电路的延迟时间影响,因此是所有ADC架构设计中转换速度最快的,转换速率可以达到GHz。由于要提高分辨率就需要成倍的增加更多的电路元器件,因此并行比较型ADC难以做到高分辨率,且受到功率和体积的限制。

特点为转换速度快,但分辨率不高,功耗大,成本高。

3.4 ∑-Δ型ADC

∑–△型ADC不直接根据抽样数据的每一个样值的大小进行量化编码,而是用前一量值与后一量值的差值即所谓的增量的大小来进行量化编码,某种意义上它是根据波形的包络线进行量化编码的。∑–△型ADC由两部分组成,第一部分为模拟∑–△调制器,第二部分为数字抽取滤波器。△表示增量,∑表示积分或求和。

单片机ADC采样

前言:

ADC是单片机中将模拟量转换为数字量的器件,我们称之为魔术转换器,简称ADC。模拟量是指变量在一定时间范围连续变化的量,数字量在时间上是不连续的,离散的。

1 ADC采样原理

将模拟量转换为数字量的过程一般可分为:采样、保持、量化、编码四个步骤。在实际的转换过程中,这些过程有时是合并进行,比如取样和保持,量化和编码可同时进行。

1.1 采样

将时间连续变化的模拟量转换为时间离散的模拟量。通过控制采样电路开关,使得连续的模拟采样信号被周期性的导通一段时间。这个周期即为ADC的采样周期。

1.2 保持

由于被测模拟信号可能一直处于变化状态,因此为了保证采样的精准性,在量化编码期间应保持被测信号不变,这就是保持的作用。比如对电压的ADC转换,采样电路开关导通后,模拟信号输入进保持电路的电容,开始充电,之后采样断开后电容中的电量被保持,等待量化操作和下一个采样脉冲到来。

1.3 量化

将采样保持后的信号量以某个“最小单位”的整数倍表示,这一过程称为量化。

常见的量化方法有四舍五入法和舍小数法。

1.3.1 四舍五入量化

假设信号量化的最小单位是A,那么把剩余 < A/2** 的部分作为0处理,把剩余 **>= A/2 的部分作为1处理。

1.3.2 舍小数量化

假设信号量化的最小单位是A,那么把剩余 < A 的部分作为0处理。

1.4 编码

把量化的结果用二进制表示的过程称为编码。

2 ADC重要参数

2.1 精度

ADC采样精度是衡量ADC采样精准的指标。通常官方的芯片数据手册上都会给出ADC在不同配置和环境下的精度数据。通常我们以偏差多少个LSB(以分辨率衡量精度)来表示ADC精度。比如下图就是ST的手册给出的ADC精度数据。

2.2 分辨率

常见的ADC有8bit、12bit、16bit等,位数反应的是ADC的分辨率。

$$Vref / 2^N$$

比如ADC的参考电压范围是3.3v,那么12bit ADC对应的分辨率为 $3.3v / 2^12 \approx 0.806mv/LSB$ ,因此分辨率约0.806mv,这是12bit ADC在参考电压3.3v所能表示的最小电压刻度,也即1LSB对应的电压值,分辨率也被用来作为衡量ADC精度的单位。

2.3 采样率

指单位时间内采集信号的次数,比如1MHz/s表示ADC一秒采集1M次。采样率越高,相同时间内采集的点数越多,对信号的还原度也就越高,但是需要处理的数据也越多。关于信号采样速率,有个奈奎斯特定律需要遵守。

2.3.1 奈奎斯特定律

奈奎斯特定理又称采样定理,当采样速率大于原始信号中最高频率的2倍以上时,采样后的数字信号可以完整的保留原始信号中的信息,否则采样后信号将会发生混叠导致失真。一般实际运用中保证采样频率是原始信号最高频率的2.56~4倍。

3 常见ADC转换器

常见的ADC转换器有下面几类。

- 转换速度最快的是:并联比较型ADC;

- 转换速度最慢的是:双积分型ADC;

- 转换精度最高的是:双积分型ADC;

- 转换精度最低的是:并联比较型ADC;

- 转换速度和精度均较高的是:逐次比较型ADC;

3.1 逐次逼近型(SAR ADC)

逐次逼近型ADC是目前单片机中应用非常广泛的一类ADC,包含1个比较器、1个DAC、1个逐次逼近寄存器、1个逻辑控制单元。SAR ADC基本原理非常简单,输入电压Vin采样保持电路后电压值被保持住,随后在比较器、DAC、逻辑控制单元作用下按照二进制搜索算法,首先将逐次逼近寄存器最高位置1,对应的DAC输出电压为Vref/2,然后比较器比较DAC的输出和采样保持住的Vin电压,如果 Vin > Vref/2 则比较器输出1,若 Vin < Vref/2 则比较器输出0。逻辑控制单元采集到比较器输出,并将其保存到逐次比较寄存器最高位MSB,随后在逻辑控制单元操控下逐次比较寄存器移动到下一位并先将其置1,逐位比较下去直到比较出所有位即完成编码工作。

以上即为4bit逐位比较ADC的量化编码过程,输出编码结果为0100b。通常N位SAR ADC需要N个比较周期,因此SAR ADC的分辨率越高,完成比较的时间越长。因此高分辨率且高采样率的SAR ADC很少见。可见功耗也与此相关,采样速率越高功耗越高。

特点为当分辨率较低时价格也较低,速率可达MHz,功耗相对也较低。在单片机中运行广泛。

3.2 积分型ADC

积分ADC通过积分器将输入电压转换成数字表示的一种ADC。其原理是把输入的模拟信号转换成与之成正比的时间间隔,然后在这个时间间隔内利用计数器对固定频率的计数脉冲进行技术,计数器的计数值就是AD转换后输出的数字量,它与输入模拟信号成正比。

积分型ADC两次积分的时间都是利用是同一个时钟和计数器,因此D表达式与时钟频率无关,其转换精度只取决于参考电压。因此积分型ADC对交流噪声的干扰有很强的抑制作用,能抑制高频噪声和固定频率的低频干扰。

特点为分辨率高,功耗低,成本低,但转换速率低。在数字电压计等高精度测量仪表中应用广泛。

3.3 并行比较型ADC

并行比较型ADC通过多个高精度电阻将Vref分为多个等级,其中每个等级分别与比较器相连作为其输入,同时比较得出每一位的值,从而实现并行转换的目的。由于是并行转换的,其转换时间只受比较器、触发器、编码电路的延迟时间影响,因此是所有ADC架构设计中转换速度最快的,转换速率可以达到GHz。由于要提高分辨率就需要成倍的增加更多的电路元器件,因此并行比较型ADC难以做到高分辨率,且受到功率和体积的限制。

特点为转换速度快,但分辨率不高,功耗大,成本高。

3.4 ∑-Δ型ADC

∑–△型ADC不直接根据抽样数据的每一个样值的大小进行量化编码,而是用前一量值与后一量值的差值即所谓的增量的大小来进行量化编码,某种意义上它是根据波形的包络线进行量化编码的。∑–△型ADC由两部分组成,第一部分为模拟∑–△调制器,第二部分为数字抽取滤波器。△表示增量,∑表示积分或求和。

特点为低速∑-Δ型ADC价格较低,高分辨率能达到24bit,内部利用高倍频过采样技术,实现数字滤波。主要运用于音频和测量。

特点为低速∑-Δ型ADC价格较低,高分辨率能达到24bit,内部利用高倍频过采样技术,实现数字滤波。主要运用于音频和测量。