一种自动捕获模拟PWM波的单片机逻辑电路

一种自动捕获模拟PWM波的单片机逻辑电路

前言:

本文介绍一种通过单片机捕获模拟PWM方波的单片机逻辑电路,这种电路的优点是捕获器件不需要CPU干预,捕获迅速且资源开销小,兼具灵活性和准确性。

1 模拟PWM捕获单片机数字电路设计

单片机能接收处理模拟PWM信号的外设有ADC和CMP(比较器),以下对比两种方式。

1.1 使用ADC捕获信号

通过ADC对模拟信号进行固定频率的连续性采样,对采样的数据进行处理从而恢复原信号,整个过程需要CPU的干预。

一种自动捕获模拟PWM波的单片机逻辑电路

前言:

本文介绍一种通过单片机捕获模拟PWM方波的单片机逻辑电路,这种电路的优点是捕获器件不需要CPU干预,捕获迅速且资源开销小,兼具灵活性和准确性。

1 模拟PWM捕获单片机数字电路设计

单片机能接收处理模拟PWM信号的外设有ADC和CMP(比较器),以下对比两种方式。

1.1 使用ADC捕获信号

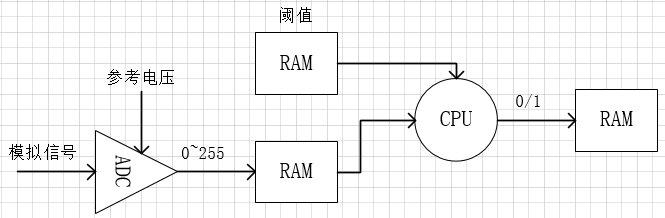

通过ADC对模拟信号进行固定频率的连续性采样,对采样的数据进行处理从而恢复原信号,整个过程需要CPU的干预。

按照奈奎斯特定律(采样定律),采样速率必须是被采信号频率的两倍以上,实际的工业使用中通常为2.5倍。

ADC外设以被采信号2.5倍的速率进行采样,将模拟量转为数字量,如8位ADC则为0~255的采样值,通过CPU的处理与阈值进行比较(阈值可以是定值或CPU实时计算的动态阈值),将比较结果二值化为0/1量存于RAM中。缺点是当被采信号是高频时如1MHz,则ADC的采样速率需达到2.5MHz,这意味着每0.4μs产生一个数据,持续采集1ms将产生400个数据,这对主频不高的CPU来说是庞大的数据量。因此建议在被采信号主频不高,连续采集时间不长的情况下使用此种方式。

1.2 使用CMP捕获信号

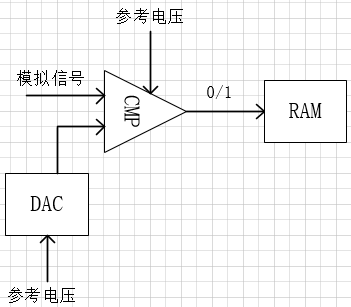

当CPU主频不高时,最好的办法是不需要CPU干预自动完成采样和二值化转换,电路设计如下。

比较器可以自动将输入的模拟信号(INP通道)与另一个通道(INM通道)进行比较,将比较结果二值化输出。比较器要实现动态阈值调整需要在INM通道使用DAC作为其输入,阈值精度要求不高时也可使用VREF的固定档位(VREF / n)。

相比较而言,使用CMP的方式可以自动完成二值化的过程,不需要CPU执行比较指令,节省了CPU,因此建议使用此种方式。为了将比较的二值化数据按序存入RAM,并且省去CPU的干预,还需要借助DMA自动转移数据。

1.3 捕获模拟PWM的数字电路设计

利用单片机实现,在比较器的INP端输入模拟信号,与单片机的模拟IO脚直连。比较器的INM端连接DAC,通过DAC设置比较器的阈值。比较器的输出结果即为模拟信号二值化的结果,此时有两种方式。

1.3.1 定时器固定频率触发CMP

通过比较器事件触发的方式在DMA作用下自动连续的将比较结果直接输出到RAM中,此时得到的是一串二进制数。这种方式还需要借助定时器的事件触发,达到固定频率的触发比较器输出结果。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按1μs速率进行比较,得到的二进制串为 11100110 。

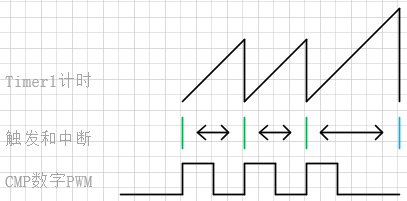

1.3.2 CMP捕获信号边沿

对于高频信号,连续对信号采样或比较会产生大量的0/1数据,对CPU来说会有大量的数据需要处理,通过比较器可以只捕捉信号的边沿(上升沿、下降沿、双边沿),再转而触发定时器从而实现捕捉边沿间隔时间的办法。这种方法不再是关注固定频率下信号的0/1值,而是关注信号边沿之间的间隔时间,从而实现了简化数据量。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按捕获上升沿间隔时间后得到的数据为 5 。数据的简化也会使得对波形细节的描述丢失,但对于一些固定序列的波形则非常适用,比如DSSS信号的PN序列。

比较器INP输入模拟PWM信号,INM则输入DAC结果,方便动态调节阈值。CMP输出比较结果,比如捕获到上升沿时比较器输出事件触发Timer1定时器,开始计时(若定时器未启动)、DMA获取当前计时值(CMP上升沿事件同时触发DMA获取Timer1计时值)、清零计时值。建议使用一个低功耗定时器LPT1控制CMP的持续工作和暂停工作时间,从而优化功耗。

每个上升沿CMP都触发Timer1启动和清零,实际第一个上升沿由关到开的启动有效;上升沿触发DMA将Timer1计时值存入RAM数组。利用Timer1计时上升沿之间的时间,利用Timer1溢出或比较中断判定信号结束。

按照奈奎斯特定律(采样定律),采样速率必须是被采信号频率的两倍以上,实际的工业使用中通常为2.5倍。

ADC外设以被采信号2.5倍的速率进行采样,将模拟量转为数字量,如8位ADC则为0~255的采样值,通过CPU的处理与阈值进行比较(阈值可以是定值或CPU实时计算的动态阈值),将比较结果二值化为0/1量存于RAM中。缺点是当被采信号是高频时如1MHz,则ADC的采样速率需达到2.5MHz,这意味着每0.4μs产生一个数据,持续采集1ms将产生400个数据,这对主频不高的CPU来说是庞大的数据量。因此建议在被采信号主频不高,连续采集时间不长的情况下使用此种方式。

1.2 使用CMP捕获信号

当CPU主频不高时,最好的办法是不需要CPU干预自动完成采样和二值化转换,电路设计如下。

一种自动捕获模拟PWM波的单片机逻辑电路

前言:

本文介绍一种通过单片机捕获模拟PWM方波的单片机逻辑电路,这种电路的优点是捕获器件不需要CPU干预,捕获迅速且资源开销小,兼具灵活性和准确性。

1 模拟PWM捕获单片机数字电路设计

单片机能接收处理模拟PWM信号的外设有ADC和CMP(比较器),以下对比两种方式。

1.1 使用ADC捕获信号

通过ADC对模拟信号进行固定频率的连续性采样,对采样的数据进行处理从而恢复原信号,整个过程需要CPU的干预。

按照奈奎斯特定律(采样定律),采样速率必须是被采信号频率的两倍以上,实际的工业使用中通常为2.5倍。

ADC外设以被采信号2.5倍的速率进行采样,将模拟量转为数字量,如8位ADC则为0~255的采样值,通过CPU的处理与阈值进行比较(阈值可以是定值或CPU实时计算的动态阈值),将比较结果二值化为0/1量存于RAM中。缺点是当被采信号是高频时如1MHz,则ADC的采样速率需达到2.5MHz,这意味着每0.4μs产生一个数据,持续采集1ms将产生400个数据,这对主频不高的CPU来说是庞大的数据量。因此建议在被采信号主频不高,连续采集时间不长的情况下使用此种方式。

1.2 使用CMP捕获信号

当CPU主频不高时,最好的办法是不需要CPU干预自动完成采样和二值化转换,电路设计如下。

比较器可以自动将输入的模拟信号(INP通道)与另一个通道(INM通道)进行比较,将比较结果二值化输出。比较器要实现动态阈值调整需要在INM通道使用DAC作为其输入,阈值精度要求不高时也可使用VREF的固定档位(VREF / n)。

相比较而言,使用CMP的方式可以自动完成二值化的过程,不需要CPU执行比较指令,节省了CPU,因此建议使用此种方式。为了将比较的二值化数据按序存入RAM,并且省去CPU的干预,还需要借助DMA自动转移数据。

1.3 捕获模拟PWM的数字电路设计

利用单片机实现,在比较器的INP端输入模拟信号,与单片机的模拟IO脚直连。比较器的INM端连接DAC,通过DAC设置比较器的阈值。比较器的输出结果即为模拟信号二值化的结果,此时有两种方式。

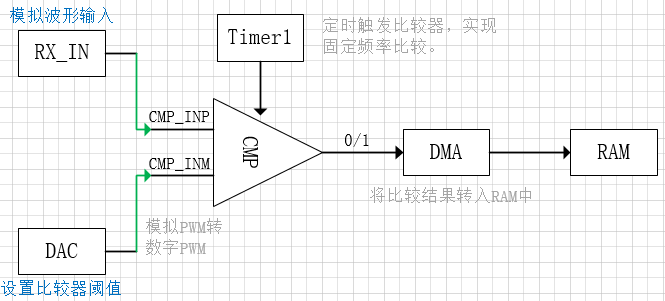

1.3.1 定时器固定频率触发CMP

通过比较器事件触发的方式在DMA作用下自动连续的将比较结果直接输出到RAM中,此时得到的是一串二进制数。这种方式还需要借助定时器的事件触发,达到固定频率的触发比较器输出结果。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按1μs速率进行比较,得到的二进制串为 11100110 。

1.3.2 CMP捕获信号边沿

对于高频信号,连续对信号采样或比较会产生大量的0/1数据,对CPU来说会有大量的数据需要处理,通过比较器可以只捕捉信号的边沿(上升沿、下降沿、双边沿),再转而触发定时器从而实现捕捉边沿间隔时间的办法。这种方法不再是关注固定频率下信号的0/1值,而是关注信号边沿之间的间隔时间,从而实现了简化数据量。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按捕获上升沿间隔时间后得到的数据为 5 。数据的简化也会使得对波形细节的描述丢失,但对于一些固定序列的波形则非常适用,比如DSSS信号的PN序列。

比较器INP输入模拟PWM信号,INM则输入DAC结果,方便动态调节阈值。CMP输出比较结果,比如捕获到上升沿时比较器输出事件触发Timer1定时器,开始计时(若定时器未启动)、DMA获取当前计时值(CMP上升沿事件同时触发DMA获取Timer1计时值)、清零计时值。建议使用一个低功耗定时器LPT1控制CMP的持续工作和暂停工作时间,从而优化功耗。

每个上升沿CMP都触发Timer1启动和清零,实际第一个上升沿由关到开的启动有效;上升沿触发DMA将Timer1计时值存入RAM数组。利用Timer1计时上升沿之间的时间,利用Timer1溢出或比较中断判定信号结束。

比较器可以自动将输入的模拟信号(INP通道)与另一个通道(INM通道)进行比较,将比较结果二值化输出。比较器要实现动态阈值调整需要在INM通道使用DAC作为其输入,阈值精度要求不高时也可使用VREF的固定档位(VREF / n)。

相比较而言,使用CMP的方式可以自动完成二值化的过程,不需要CPU执行比较指令,节省了CPU,因此建议使用此种方式。为了将比较的二值化数据按序存入RAM,并且省去CPU的干预,还需要借助DMA自动转移数据。

1.3 捕获模拟PWM的数字电路设计

利用单片机实现,在比较器的INP端输入模拟信号,与单片机的模拟IO脚直连。比较器的INM端连接DAC,通过DAC设置比较器的阈值。比较器的输出结果即为模拟信号二值化的结果,此时有两种方式。

1.3.1 定时器固定频率触发CMP

通过比较器事件触发的方式在DMA作用下自动连续的将比较结果直接输出到RAM中,此时得到的是一串二进制数。这种方式还需要借助定时器的事件触发,达到固定频率的触发比较器输出结果。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按1μs速率进行比较,得到的二进制串为 11100110 。

一种自动捕获模拟PWM波的单片机逻辑电路

前言:

本文介绍一种通过单片机捕获模拟PWM方波的单片机逻辑电路,这种电路的优点是捕获器件不需要CPU干预,捕获迅速且资源开销小,兼具灵活性和准确性。

1 模拟PWM捕获单片机数字电路设计

单片机能接收处理模拟PWM信号的外设有ADC和CMP(比较器),以下对比两种方式。

1.1 使用ADC捕获信号

通过ADC对模拟信号进行固定频率的连续性采样,对采样的数据进行处理从而恢复原信号,整个过程需要CPU的干预。

按照奈奎斯特定律(采样定律),采样速率必须是被采信号频率的两倍以上,实际的工业使用中通常为2.5倍。

ADC外设以被采信号2.5倍的速率进行采样,将模拟量转为数字量,如8位ADC则为0~255的采样值,通过CPU的处理与阈值进行比较(阈值可以是定值或CPU实时计算的动态阈值),将比较结果二值化为0/1量存于RAM中。缺点是当被采信号是高频时如1MHz,则ADC的采样速率需达到2.5MHz,这意味着每0.4μs产生一个数据,持续采集1ms将产生400个数据,这对主频不高的CPU来说是庞大的数据量。因此建议在被采信号主频不高,连续采集时间不长的情况下使用此种方式。

1.2 使用CMP捕获信号

当CPU主频不高时,最好的办法是不需要CPU干预自动完成采样和二值化转换,电路设计如下。

比较器可以自动将输入的模拟信号(INP通道)与另一个通道(INM通道)进行比较,将比较结果二值化输出。比较器要实现动态阈值调整需要在INM通道使用DAC作为其输入,阈值精度要求不高时也可使用VREF的固定档位(VREF / n)。

相比较而言,使用CMP的方式可以自动完成二值化的过程,不需要CPU执行比较指令,节省了CPU,因此建议使用此种方式。为了将比较的二值化数据按序存入RAM,并且省去CPU的干预,还需要借助DMA自动转移数据。

1.3 捕获模拟PWM的数字电路设计

利用单片机实现,在比较器的INP端输入模拟信号,与单片机的模拟IO脚直连。比较器的INM端连接DAC,通过DAC设置比较器的阈值。比较器的输出结果即为模拟信号二值化的结果,此时有两种方式。

1.3.1 定时器固定频率触发CMP

通过比较器事件触发的方式在DMA作用下自动连续的将比较结果直接输出到RAM中,此时得到的是一串二进制数。这种方式还需要借助定时器的事件触发,达到固定频率的触发比较器输出结果。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按1μs速率进行比较,得到的二进制串为 11100110 。

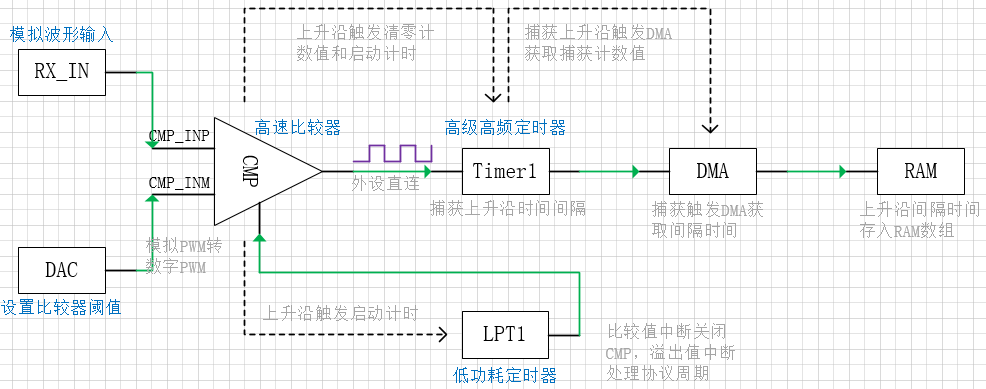

1.3.2 CMP捕获信号边沿

对于高频信号,连续对信号采样或比较会产生大量的0/1数据,对CPU来说会有大量的数据需要处理,通过比较器可以只捕捉信号的边沿(上升沿、下降沿、双边沿),再转而触发定时器从而实现捕捉边沿间隔时间的办法。这种方法不再是关注固定频率下信号的0/1值,而是关注信号边沿之间的间隔时间,从而实现了简化数据量。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按捕获上升沿间隔时间后得到的数据为 5 。数据的简化也会使得对波形细节的描述丢失,但对于一些固定序列的波形则非常适用,比如DSSS信号的PN序列。

比较器INP输入模拟PWM信号,INM则输入DAC结果,方便动态调节阈值。CMP输出比较结果,比如捕获到上升沿时比较器输出事件触发Timer1定时器,开始计时(若定时器未启动)、DMA获取当前计时值(CMP上升沿事件同时触发DMA获取Timer1计时值)、清零计时值。建议使用一个低功耗定时器LPT1控制CMP的持续工作和暂停工作时间,从而优化功耗。

每个上升沿CMP都触发Timer1启动和清零,实际第一个上升沿由关到开的启动有效;上升沿触发DMA将Timer1计时值存入RAM数组。利用Timer1计时上升沿之间的时间,利用Timer1溢出或比较中断判定信号结束。

1.3.2 CMP捕获信号边沿

对于高频信号,连续对信号采样或比较会产生大量的0/1数据,对CPU来说会有大量的数据需要处理,通过比较器可以只捕捉信号的边沿(上升沿、下降沿、双边沿),再转而触发定时器从而实现捕捉边沿间隔时间的办法。这种方法不再是关注固定频率下信号的0/1值,而是关注信号边沿之间的间隔时间,从而实现了简化数据量。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按捕获上升沿间隔时间后得到的数据为 5 。数据的简化也会使得对波形细节的描述丢失,但对于一些固定序列的波形则非常适用,比如DSSS信号的PN序列。

一种自动捕获模拟PWM波的单片机逻辑电路

前言:

本文介绍一种通过单片机捕获模拟PWM方波的单片机逻辑电路,这种电路的优点是捕获器件不需要CPU干预,捕获迅速且资源开销小,兼具灵活性和准确性。

1 模拟PWM捕获单片机数字电路设计

单片机能接收处理模拟PWM信号的外设有ADC和CMP(比较器),以下对比两种方式。

1.1 使用ADC捕获信号

通过ADC对模拟信号进行固定频率的连续性采样,对采样的数据进行处理从而恢复原信号,整个过程需要CPU的干预。

按照奈奎斯特定律(采样定律),采样速率必须是被采信号频率的两倍以上,实际的工业使用中通常为2.5倍。

ADC外设以被采信号2.5倍的速率进行采样,将模拟量转为数字量,如8位ADC则为0~255的采样值,通过CPU的处理与阈值进行比较(阈值可以是定值或CPU实时计算的动态阈值),将比较结果二值化为0/1量存于RAM中。缺点是当被采信号是高频时如1MHz,则ADC的采样速率需达到2.5MHz,这意味着每0.4μs产生一个数据,持续采集1ms将产生400个数据,这对主频不高的CPU来说是庞大的数据量。因此建议在被采信号主频不高,连续采集时间不长的情况下使用此种方式。

1.2 使用CMP捕获信号

当CPU主频不高时,最好的办法是不需要CPU干预自动完成采样和二值化转换,电路设计如下。

比较器可以自动将输入的模拟信号(INP通道)与另一个通道(INM通道)进行比较,将比较结果二值化输出。比较器要实现动态阈值调整需要在INM通道使用DAC作为其输入,阈值精度要求不高时也可使用VREF的固定档位(VREF / n)。

相比较而言,使用CMP的方式可以自动完成二值化的过程,不需要CPU执行比较指令,节省了CPU,因此建议使用此种方式。为了将比较的二值化数据按序存入RAM,并且省去CPU的干预,还需要借助DMA自动转移数据。

1.3 捕获模拟PWM的数字电路设计

利用单片机实现,在比较器的INP端输入模拟信号,与单片机的模拟IO脚直连。比较器的INM端连接DAC,通过DAC设置比较器的阈值。比较器的输出结果即为模拟信号二值化的结果,此时有两种方式。

1.3.1 定时器固定频率触发CMP

通过比较器事件触发的方式在DMA作用下自动连续的将比较结果直接输出到RAM中,此时得到的是一串二进制数。这种方式还需要借助定时器的事件触发,达到固定频率的触发比较器输出结果。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按1μs速率进行比较,得到的二进制串为 11100110 。

1.3.2 CMP捕获信号边沿

对于高频信号,连续对信号采样或比较会产生大量的0/1数据,对CPU来说会有大量的数据需要处理,通过比较器可以只捕捉信号的边沿(上升沿、下降沿、双边沿),再转而触发定时器从而实现捕捉边沿间隔时间的办法。这种方法不再是关注固定频率下信号的0/1值,而是关注信号边沿之间的间隔时间,从而实现了简化数据量。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按捕获上升沿间隔时间后得到的数据为 5 。数据的简化也会使得对波形细节的描述丢失,但对于一些固定序列的波形则非常适用,比如DSSS信号的PN序列。

比较器INP输入模拟PWM信号,INM则输入DAC结果,方便动态调节阈值。CMP输出比较结果,比如捕获到上升沿时比较器输出事件触发Timer1定时器,开始计时(若定时器未启动)、DMA获取当前计时值(CMP上升沿事件同时触发DMA获取Timer1计时值)、清零计时值。建议使用一个低功耗定时器LPT1控制CMP的持续工作和暂停工作时间,从而优化功耗。

每个上升沿CMP都触发Timer1启动和清零,实际第一个上升沿由关到开的启动有效;上升沿触发DMA将Timer1计时值存入RAM数组。利用Timer1计时上升沿之间的时间,利用Timer1溢出或比较中断判定信号结束。

比较器INP输入模拟PWM信号,INM则输入DAC结果,方便动态调节阈值。CMP输出比较结果,比如捕获到上升沿时比较器输出事件触发Timer1定时器,开始计时(若定时器未启动)、DMA获取当前计时值(CMP上升沿事件同时触发DMA获取Timer1计时值)、清零计时值。建议使用一个低功耗定时器LPT1控制CMP的持续工作和暂停工作时间,从而优化功耗。

一种自动捕获模拟PWM波的单片机逻辑电路

前言:

本文介绍一种通过单片机捕获模拟PWM方波的单片机逻辑电路,这种电路的优点是捕获器件不需要CPU干预,捕获迅速且资源开销小,兼具灵活性和准确性。

1 模拟PWM捕获单片机数字电路设计

单片机能接收处理模拟PWM信号的外设有ADC和CMP(比较器),以下对比两种方式。

1.1 使用ADC捕获信号

通过ADC对模拟信号进行固定频率的连续性采样,对采样的数据进行处理从而恢复原信号,整个过程需要CPU的干预。

按照奈奎斯特定律(采样定律),采样速率必须是被采信号频率的两倍以上,实际的工业使用中通常为2.5倍。

ADC外设以被采信号2.5倍的速率进行采样,将模拟量转为数字量,如8位ADC则为0~255的采样值,通过CPU的处理与阈值进行比较(阈值可以是定值或CPU实时计算的动态阈值),将比较结果二值化为0/1量存于RAM中。缺点是当被采信号是高频时如1MHz,则ADC的采样速率需达到2.5MHz,这意味着每0.4μs产生一个数据,持续采集1ms将产生400个数据,这对主频不高的CPU来说是庞大的数据量。因此建议在被采信号主频不高,连续采集时间不长的情况下使用此种方式。

1.2 使用CMP捕获信号

当CPU主频不高时,最好的办法是不需要CPU干预自动完成采样和二值化转换,电路设计如下。

比较器可以自动将输入的模拟信号(INP通道)与另一个通道(INM通道)进行比较,将比较结果二值化输出。比较器要实现动态阈值调整需要在INM通道使用DAC作为其输入,阈值精度要求不高时也可使用VREF的固定档位(VREF / n)。

相比较而言,使用CMP的方式可以自动完成二值化的过程,不需要CPU执行比较指令,节省了CPU,因此建议使用此种方式。为了将比较的二值化数据按序存入RAM,并且省去CPU的干预,还需要借助DMA自动转移数据。

1.3 捕获模拟PWM的数字电路设计

利用单片机实现,在比较器的INP端输入模拟信号,与单片机的模拟IO脚直连。比较器的INM端连接DAC,通过DAC设置比较器的阈值。比较器的输出结果即为模拟信号二值化的结果,此时有两种方式。

1.3.1 定时器固定频率触发CMP

通过比较器事件触发的方式在DMA作用下自动连续的将比较结果直接输出到RAM中,此时得到的是一串二进制数。这种方式还需要借助定时器的事件触发,达到固定频率的触发比较器输出结果。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按1μs速率进行比较,得到的二进制串为 11100110 。

1.3.2 CMP捕获信号边沿

对于高频信号,连续对信号采样或比较会产生大量的0/1数据,对CPU来说会有大量的数据需要处理,通过比较器可以只捕捉信号的边沿(上升沿、下降沿、双边沿),再转而触发定时器从而实现捕捉边沿间隔时间的办法。这种方法不再是关注固定频率下信号的0/1值,而是关注信号边沿之间的间隔时间,从而实现了简化数据量。比如一段模拟PWM的波形为3μs的高电平,2μs低电平,2μs高电平,1μs低电平,则按捕获上升沿间隔时间后得到的数据为 5 。数据的简化也会使得对波形细节的描述丢失,但对于一些固定序列的波形则非常适用,比如DSSS信号的PN序列。

比较器INP输入模拟PWM信号,INM则输入DAC结果,方便动态调节阈值。CMP输出比较结果,比如捕获到上升沿时比较器输出事件触发Timer1定时器,开始计时(若定时器未启动)、DMA获取当前计时值(CMP上升沿事件同时触发DMA获取Timer1计时值)、清零计时值。建议使用一个低功耗定时器LPT1控制CMP的持续工作和暂停工作时间,从而优化功耗。

每个上升沿CMP都触发Timer1启动和清零,实际第一个上升沿由关到开的启动有效;上升沿触发DMA将Timer1计时值存入RAM数组。利用Timer1计时上升沿之间的时间,利用Timer1溢出或比较中断判定信号结束。

每个上升沿CMP都触发Timer1启动和清零,实际第一个上升沿由关到开的启动有效;上升沿触发DMA将Timer1计时值存入RAM数组。利用Timer1计时上升沿之间的时间,利用Timer1溢出或比较中断判定信号结束。