第十四章——嵌入式系统总线和通讯接口

第十四章——嵌入式系统总线和通讯接口

前言:

计算机第十四章节主要知识点。

1 知识点介绍

- 串行接口基本原理与结构

- 并行接口基本原理与结构

- PCI接口基本原理与结构

- USB接口基本原理与结构

- SPI接口基本原理与结构

- IIC接口基本原理与结构

- 网络接口基本原理与结构

- 总线分类

2 串行接口基本原理与结构

- 串行通信概述

- RS-232C串行接口

- RS-422串行通信接口

- RS-485串行总线接口

2.1 串行通信概述

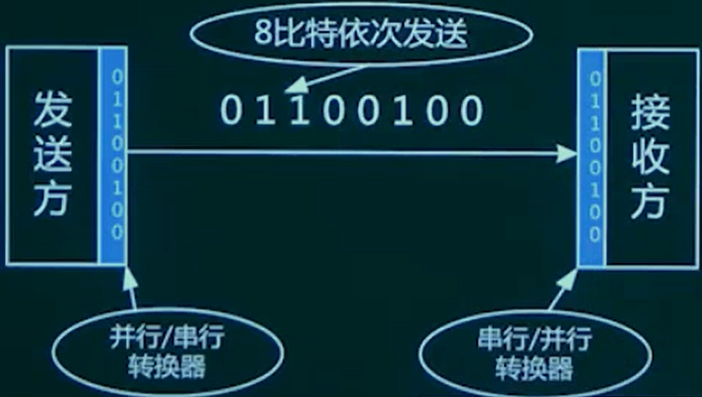

串行通信:数据是一位一位地进行传输的,在传输中每一位数据都占据一个固定的时间长度。

优点。

- 传输线少、成本低

- 特别适合远距离传送

缺点。

- 速度慢

第十四章——嵌入式系统总线和通讯接口

前言:

计算机第十四章节主要知识点。

1 知识点介绍

- 串行接口基本原理与结构

- 并行接口基本原理与结构

- PCI接口基本原理与结构

- USB接口基本原理与结构

- SPI接口基本原理与结构

- IIC接口基本原理与结构

- 网络接口基本原理与结构

- 总线分类

2 串行接口基本原理与结构

- 串行通信概述

- RS-232C串行接口

- RS-422串行通信接口

- RS-485串行总线接口

2.1 串行通信概述

串行通信:数据是一位一位地进行传输的,在传输中每一位数据都占据一个固定的时间长度。

优点。

- 传输线少、成本低

- 特别适合远距离传送

缺点。

- 速度慢

2.2 串行通信模式

2.2.1 单工

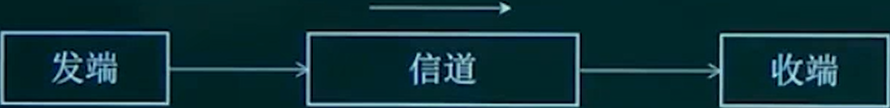

串行数据传送有3种基本的通信模式:单工、半双工、全双工通信。

单工通信:数据仅能从设备A到设备B进行单一方向的传输。如遥控、遥测等。

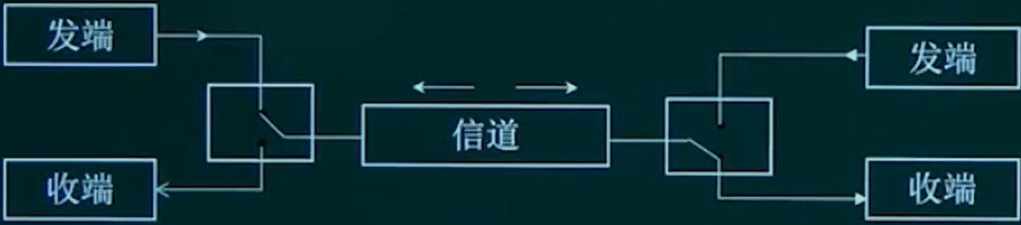

2.2.2 半双工

半双工通信:数据可以从设备A到设备B进行传输,也可以从设备B到设备A进行传输,但不能在同一时刻进行双向传输。如:对讲机。

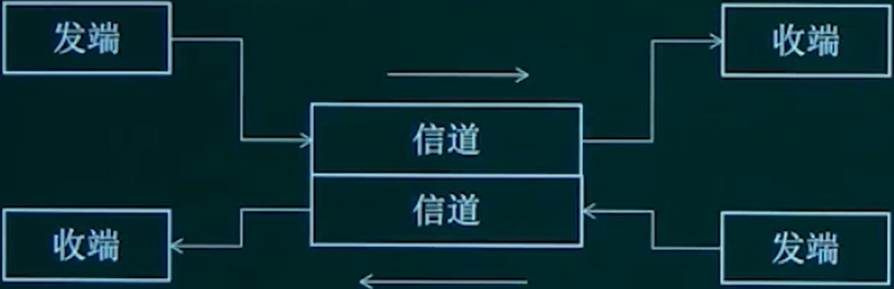

2.2.3 全双工

全双工通信:数据可以在同一时刻从设备A传输到设备B,或从设备B传输到设备A,即可以同时双向传输。如电话。

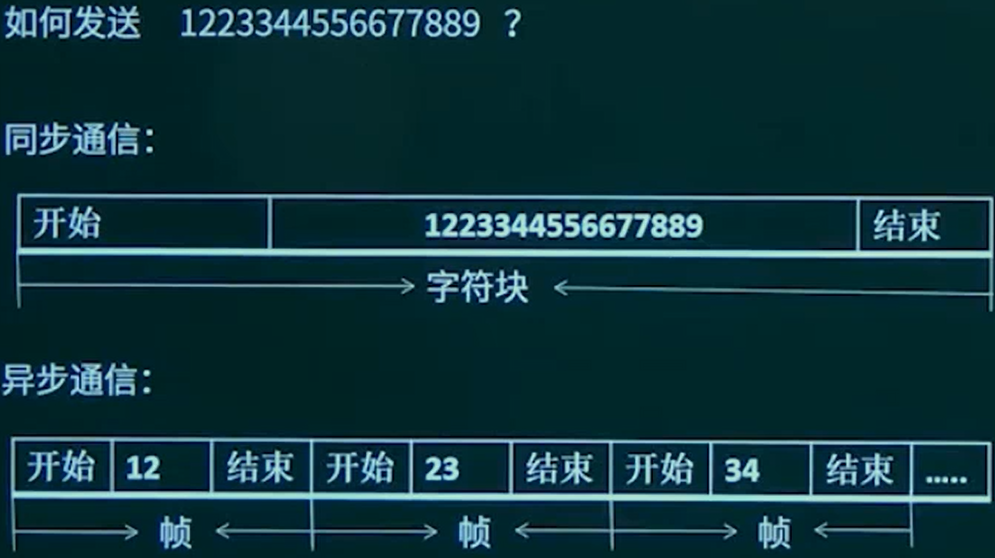

2.2.4 串行通信异步

串行通信在信息格式上可以分为:异步通信和同步通信方式。

异步通信方式。

- 是指通信的发送与接收设备使用各自的时钟,控制数据的发送和接收过程。

- 为使双方的收发协调,要求发送和接收设备的时钟尽可能一致。

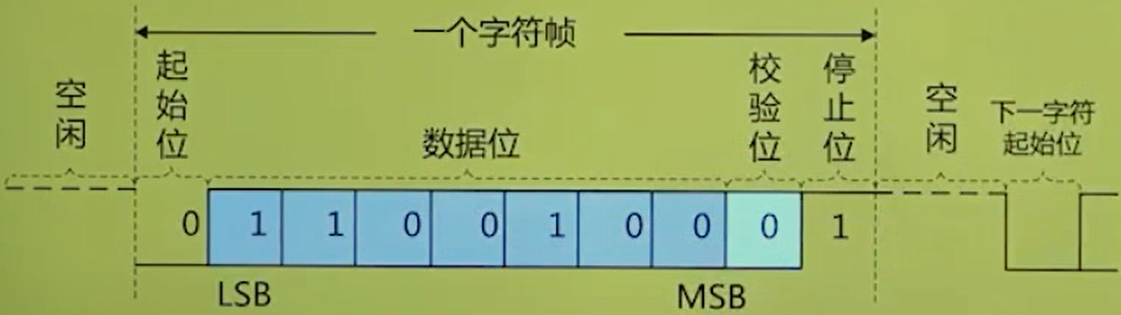

异步通信方式。

- 数据是一帧一帧传送的,没帧数据包含有起始位(“0”)、数据位、奇偶校验位和停止位(“1”),每帧数据的传送靠起始位来同步。

- 一帧数据的各位代码间的时间间隔是固定的,而相邻两帧的数据其时间间隔是不固定的。

- 在异步通信的数据传送中,传输线上允许空字符。

字符格式。

- 异步通信对字符格式、波特率、校验位有确定的要求。

字符格式。

- 每个字符传送时,必须前面加一位起始位,后面加上1、1.5或2位停止位。

- 例如ASCII码传送时,一帧数据的组成是:前面1个起始位,接着7位ASCII编码,再接着一位奇偶校验位,最后一位停止位,共10位。

2.2.5 波特率和校验位

波特率。

- 传送数据位的速率称为波特率,用位/秒(bit/s)来表示,称之为波特。

- 例如,数据传送的速率为120字符/秒,每帧包括10个数据位,则传送波特率为: $10 \times 120 = 1200b/s = 1200波特$

- 异步通信的波特率的数值通常为:150、300、600、1200、2400、4800、9600、14400、28800等,数值成倍数变化。

校验位。

- 偶校验就是要使字符加上校验位有偶数个“1”。

- 奇校验就是要使字符加上校验位有奇数个“1”。

- 例如数据“00010011”,共有奇数个“1”,偶校验时,则校验位就置为“1”,奇校验时,则校验位就置为“0”。

2.2.6 串行异步特点

异步通信的特点。

- 不要求收发双方时钟的严格一致,实现容易,设备开销较小。

- 但每个字符要附加2~3位用于起始,各帧之间还有间隔,因此传输效率不高。实际使用率只有约80%。

2.2.7 串行通信同步

同步通信。

- 是一种比特同步通信技术,要求收发双方具有同频同相的同步时钟信号,只需在传送报文的最前面附加特定的同步字符,使收发双方建立同步,此后便在同步时钟的控制下逐位发送/接收。

- 同步传输采用字符块的方式,减少每一个字符的控制和错误检测数据位,因而可以具有较高的传输速率。

- 即将许多字符聚集成一字符块后,在每块信息之前要加上1~2个同步字符,字符块之后再加入适当的错误检测数据才传送出去。

特点。

- 数据传输速率较高。

- 但要求发送方时钟和接收方时钟保持严格同步。

2.2.8 串口同步和异步发送

2.3 RS-232C串行接口

2.3.1 接口规格

RS-232C是美国电子工业协会(EIA)制定的一种串行通信接口标准。

RS-232C接口规格。

- EIA所制定的传送电气规格如下表所示。

- RS-232C通常以±12v的电压来驱动信号线,TTL标准与RS-232C标准之间的电平转换电路通常采用集成电路芯片实现,如M2AX23等。

| 状态 | L(Low) | H(Hight) |

|---|---|---|

| 电压范围 | -25~-3v | +3v~25v |

| 负逻辑 | 1 | 0 |

2.3.2 接口信号

EIA制定的RS-232C接口与外界的相连采用25芯(DB-25)和9芯(DB-9)D型插接件,实际应用中,并不是每只引脚信号都必须用到。

2.3.3 引脚功能

RS-232C DB-9各引脚功能如下。

| 引脚号 | 符号表示 | 名称 | 说明 |

|---|---|---|---|

| 1 | CD | 载波检测 | 主要用于Modem通知计算机其处于在线状态,即Modem检测到拨号音 |

| 2 | RXD | 接收数据线 | 用于接收外部设备送来的数据 |

| 3 | TXD | 发送数据线 | 用于将计算机的数据发送给外部设备 |

| 4 | DTR | 数据终端 | 当次引脚高电平时,通知Modem可以进行数据传输,计算机已经准备好 |

| 5 | SG | 信号地 | |

| 6 | DSR | 数据设备就绪 | 此引脚为高电平时,通知计算机Modem已经准备好,可以进行数据通信 |

| 7 | RTS | 请求发送 | 此引脚由计算机来控制,用以通知Modem马上传送数据至计算机,否则Modem将收到的数据暂时放入缓冲区中 |

| 8 | CTS | 允许发送 | 此引脚由Modem控制,用以通知计算机将要传送的数据送至Modem |

| 9 | RI | 振铃提示 | Modem通知计算机有呼叫进来,是否接听呼叫由计算机决定 |

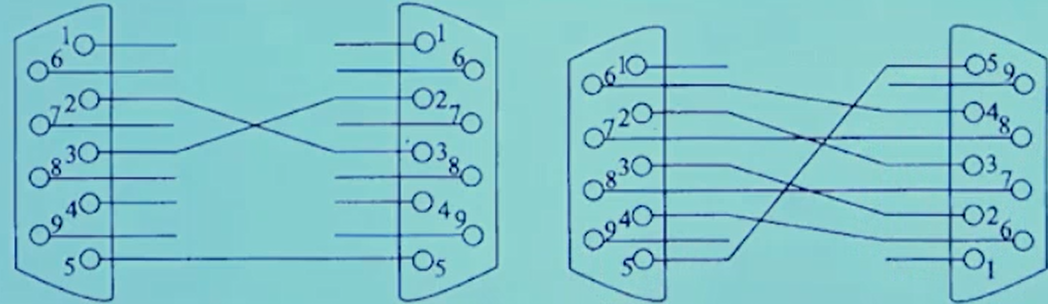

2.3.4 连接方式

RS-232C的基本连接方式。

- 计算机利用RS-232C接口进行串口通信,有简单连接和完全连接两种连接方式

- 简单连接又称三线连接,即只连接发送数据线、接收数据线和信号地,实现全双工通信

- 如果应用中还需要使用RS-232C的控制信号,则采用完全连接方式。

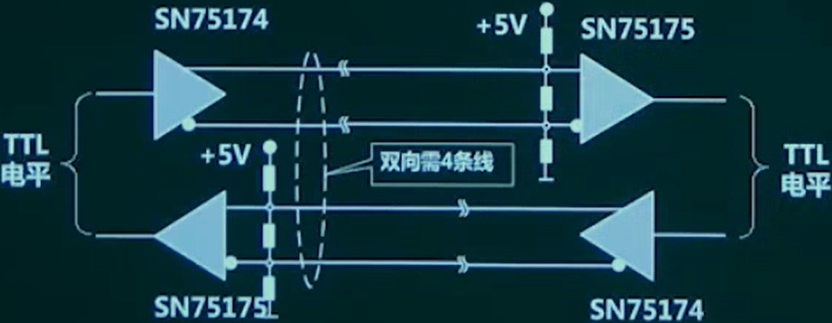

2.4 RS-422串行接口

RS-422标准是RS-232的改进型,是一种可单机发送多机接收的平衡传输规范,传输速率可达10Mb/s。采用差分传输方式,也称平衡传输。

- 允许在相同传输线上连接多个接收节点,最多可接10个节点,即一个主设备(Master),其余10个为从设备(Slave),从设备之间不能通信。

- 支持一点对多点的双向通信。RS-422四线接口由于采用单独的发送和接收通道,因此不必控制数据方向,各装置之间任何必须的信号交换均可以按软件方式(XON/XOFF握手)或硬件方式(一对单独的双绞线)实现。

RS-422的最大传输距离为4000英尺(约1219m),最大传输速率为10Mb/s。

- 传输速率与平衡双绞线的长度有关,只有在很短的距离下才能获得最高传输速率

- 在最大传输距离时,传输速率为100kb/s

- 一般100m长的双绞线上所能获得的最大传输速率仅为1Mb/s

RS-422需要在传输电缆的最远端连接一个电阻,要求电阻阻值约等于传输电缆的特性阻抗。

- 在短距离(300m以下)传输时可以不连接电阻。

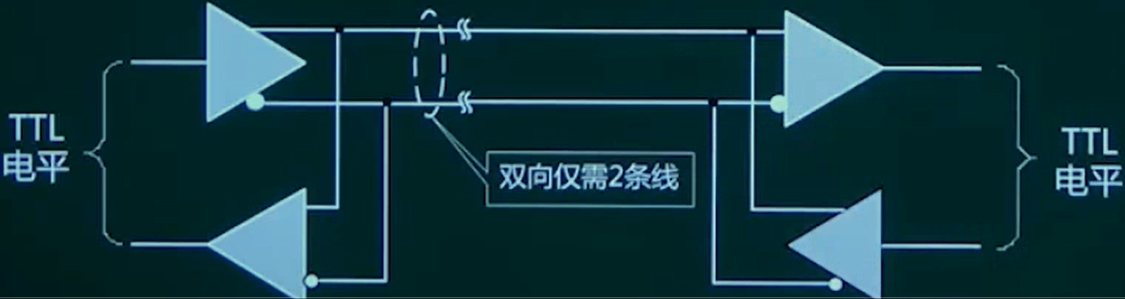

2.5 RS-485串行接口

在RS-422的基础上,为扩展应用范围,EIA制定了RS-485标准,增加了多点、双向通信能力。

- 在通信距离为几十米至上千米时,通常采用RS-485接收器

- RS-485接收器采用平衡发送和差分接收

- 即在发送端,驱动器将TTL电平信号转换成差分信号输出,在接收端,接收器将差分信号变成TTL电平,因此具有抑制共模干扰的能力。

- 接收器能够检测低达200mv的电压,具有高的灵敏度,故数据传输距离可达千米以上。

RS-485可以采用二线与四线方式,二线制可以实现真正的多点双向通信。

- 采用四线连接时,与RS-422一样只能实现点对点的通信,即只能有一个主设备,其余为从设备。

- RS-485可以连接多达32个设备

RS-485的共模输出电压在-7~+12v之间,接收器最小输入阻抗为12kΩ。

RS-485满足所有RS-422的规范,所以RS-485的驱动器可以在RS-422网络中应用。

RS-485的最大传输速率为10Mb/s。在最大传输距离时,传输速率为100kb/s。

RS-485需要两个终端电阻,接在传输总线的两端,要求电阻阻值约等于传输电缆的特性阻抗。

- 在短距离传输(在300m以下)时可不需终端电阻。

2.6 例题

- 使用串行总线传输数据时,被传输的数据(D)。

A. 在发送设备和接收设备中都是进行串行到并行的变换

B. 在发送设备和接收设备中都是进行并行到串行的变换

C. 在发送设备中进行串行到并行的变换,接收设备中进行并行到串行的变换

D. 在发送设备中进行并行到串行的变换,接收设备中进行串行到并行的变换

3 并行接口基本原理与结构

- 并行接口分类

- 并行总线

3.1 并行接口基本概念

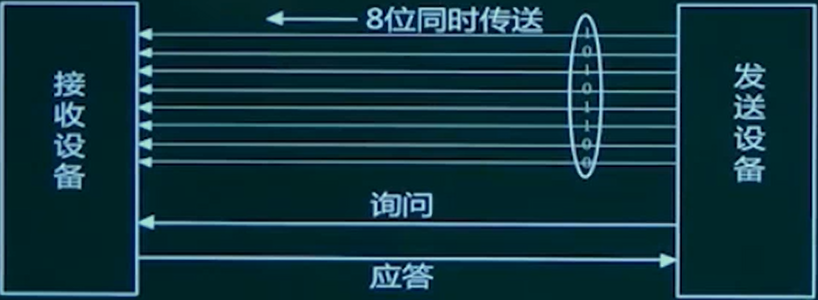

并行通信通常是将数据字节的各位用多条数据线同时进行传送。

- 一般用来连接打印机、扫描仪等,所以又称打印口。

特定。

- 控制简单,传输速度快

- 由于传输线较多,长距离传送时成本高且接收方的各位同时接收存在的困难。

3.2 并行接口分类

并行接口可以分为。

- SPP(标准并口)

- EPP(增强型并口)

- ECP(扩展型并口)

3.3 并行总线分类

&emsep; 并行总线分为。

- 标准并行总线

- 非标准并行总线

常用的并行标准总线:IEEE488总线和SCSI总线。

总线是一种高性能非标准的通用多用户并行总线。

3.4 并行总线IEE488

IEEE488总线。

- 又称GPIB总线(General Purpose Interface Bus,通用接口总线)

- 位并行、字节串行双向异步方式传输信号

- 总线方式连接,仪器设备直接并联于总线上,总线上最多可连接15台设备

- 最大传输距离为20m,信号传输速度一般为500kb/s,最大传输速度为1Mb/s

- 广泛应用在仪器、仪表、测控领域

3.5 并行总线SCSI和MXI

SCSI(Small Computer System Interface,小型计算机系统接口)总线。

- 速度可达5Mb/s,传输距离6m

- 传输速率很高

- 普通用作计算机的高速外设总线,如连接高速硬盘驱动器

MXI总线(Multi-system Extension Interface bus,多系统扩展接口总线)。

- 是一种高性能非标准的通用多用户并行总线

- 32位高速并行总线

- 最高速度可达23Mb/s,传输距离20m

- 用作计算机与测控机箱的互连

3.6 例题

- 串行总线与并行总线比,(C)。

A. 串行总线成本高,速度快

B. 串行总线成本高,速度慢

C. 并行总线成本高,速度快

D. 并行总线成本低,速度快

- 信息可以在两个方向上同时传输的总线属于(C)。

A. 单工总线

B. 半双工总线

C. 全双工总线

D. 单向总线

- 以下关于总线的叙述中,不正确的是(C)。

A. 并行总线适合近距离高速数据传输

B. 串行总线适合长距离数据传输

C. 单总线结构在一个总线上适合不同种类的设备,设计简单且性能很高

D. 专用总线在设计上可以与连接设备实现最佳匹配

4 PCI接口基本原理与结构

- PCI接口基本结构

4.1 PCI接口基本结构

PCI(Peripheral Component Interconnect,外围设备互连)总线是由Intel公司推出的一种局部总线,是当前用于系统扩展最流行的总线之一。

PCI总线是地址、数据多路复用的高性能32位和64位总线,是微处理器与外围控制部件、外围附加板之间的互连机构。

PCI定义了32位数据总线,并且可扩展为64位。总线速度有32MHz和66MHz两种。

- 改良的PCI系统PCI-X,数据传输速度最高可以达到64位@133MHz

- PCI总线主板插槽的体积比ISA总线插槽小,支持突发读写操作(突发数据传输),可同时支持多组外围设备

与ISA总线不同,PCI总线的地址总线与数据总线是分时复用的,支持即插即用(PNP:Plug-and-Play)、中断共享等功能。

PCI总线在数据传输时,由一个PCI设备做发起者(称为Master、Initator),而另一个PCI设备做目标(称为Slave、Target)。

- 总线上所有时序的产生与控制都由Master发起

- PCI总线在同一时刻只能供一对设备完成传输,要求有一个仲裁机构来决定谁有权拿到总线的主控权

4.1.1 例题

- 关于PCI总线,下列说法不正确的是(A)。

A. PCI总线是地址、数据多路复用的一种总线,不支持即插即用,支持中断共享功能

B. PCI定义了32位数据总线,也可扩展为64位总线

C. PCI总线在数据传输时,由一个PCI设备做发起者,而另一个PCI设备做目标

D. PCI总线要求有一个仲裁机构来决定谁有权拿到总线的主控权,所以在同一时刻只能供一对设备完成传输

- 在以下描述中PCI总线的基本概念中,正确的表述有(B)、(E)、(F)、(G)、(J)、(K)。

A. PCI总线是一个与处理器有关的高速外围总线

B. PCI总线的基本传输机制是触发传输

C. PCI设备一定是主设备

D. PCI的物理地址与其他总线一样,是由内存地址空间和I/O地址组成

E. PCI设备的地址译码不能对配置空间直接寻址

F. PCI设备识别主要是对开发商代码和设备代码进行识别

G. 访问配置空间时,PCI桥应提供IDSEL信号以选择PCI设备

H. 系统中只允许有一条PCI总线

I. PCI总线是高速串行总线

J. PCI总线有3种桥,即HOST/PCI桥,PCI/PCI桥,PCI/LEGACY桥

K. PCI桥是可以把一条总线的地址空间映射到另一条总线的地址空间

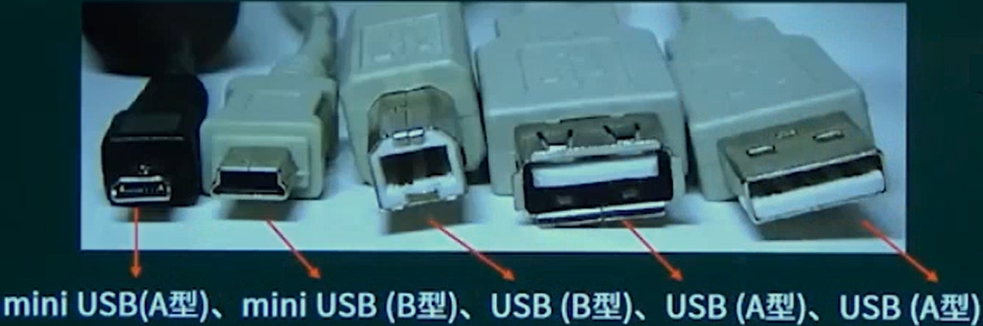

5 USB接口基本原理与结构

- USB总线的主要性能特点

- 物理接口

USB(Universal Serial Bus,通用串行总线)是由Compaq、HP、Intel、Lucent、Microsoft、NEC和Philips公司制定的连接计算机与外围设备的机外串行总线。

- 最多可连接127个设备

- 用于多种嵌入式系统设备的数据通信。如移动硬盘、PDA

5.1 热插拔

USB提供机箱外的热插拔功能,连接外设不必再打开机箱,也不必关闭主机电源,USB可智能地识别USB链上外围设备的动态插入或拆除,具有自动配置和重新配置外设的能力,连接设备方便,使用简单。

可连接多个外部设备。

- 每个USB系统中有1个主机,USB总线采用“级联”方式可连续多个外部设备。

- 每个USB设备用一个USB插头连接到上一个USB设备的USB插座上,而其本身又提供一或多个USB插座供一下一个或多个USB设备连接使用。

- 这种多重连接是通过集线器(Hub)来实现的,整个USB网络中最多可连接127个设备,支持多个设备同时操作

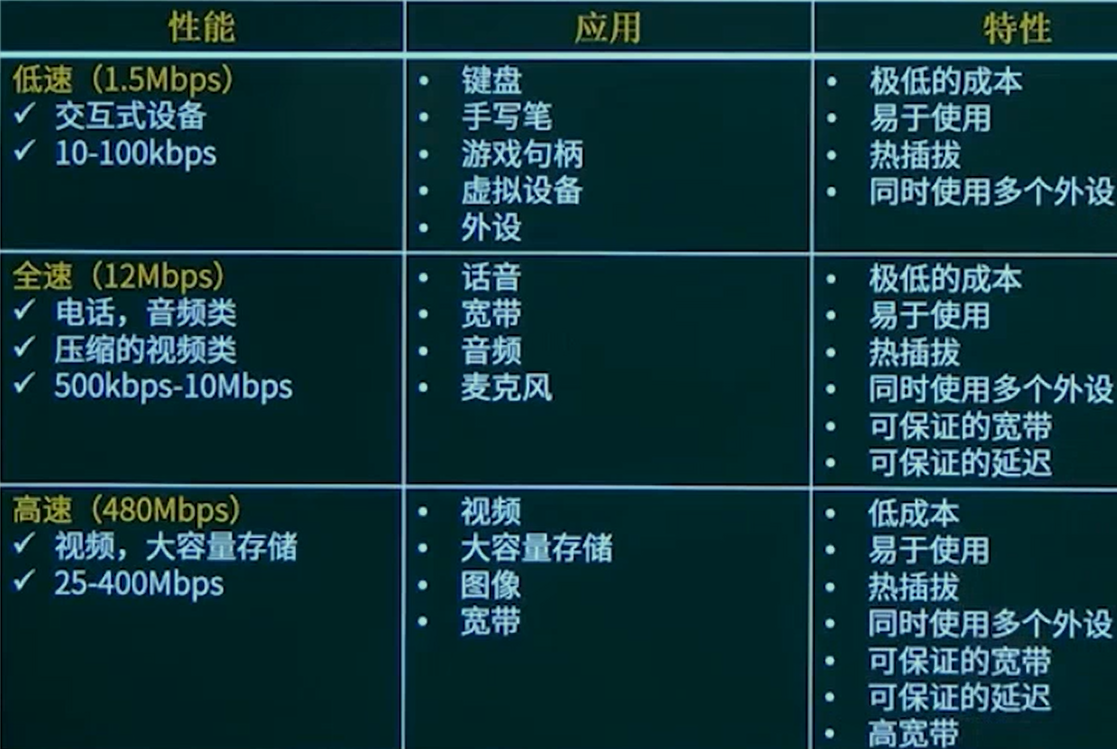

5.2 USB总线的主要性能特点

可同时支持不同同步传输方式和速率的设备。

- 可同时支持同步传输和异步传输两种传输方式

- 可同时支持不同速率的设备,速率最高可达几百Mb/s

- 支持主机与设备之间的多数据流和多消息流传输,且支持同步和异步传输类型

- 提供了四种不同的数据传输类型:控制传输、数据传输、中断数据传输和同步数据传输

较强的纠错能力。

- USB系统可实时地管理设备插拔

- 在USB协议中包括了传输错误管理、错误恢复等功能,同时根据不同的传输类型来处理传输错误

低成本的电缆和连接器。

- USB采用统一的4引脚插头和一根四芯的电缆传送信号和电源

- 电缆长度可达5m

总线供电。

- USB总线可以为连接在其上的设备提供5v电压/100mA电流的供电,最大可提供500mA的电流

- USB设备也可采用自供电方式,可以通过电池或其他的电力设备

- 支持节约能源的挂机和唤醒模式

5.3 USB总线的应用

5.4 USB总线物理接口

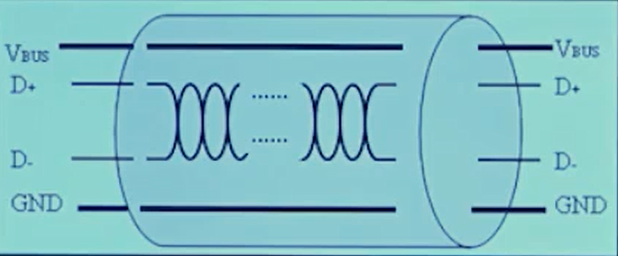

USB总线的电缆有一对标准尺寸的双绞信号线和一对标准尺寸的电源线,共4根导线。

| 连接序号 | 信号名称 | 典型连接线 |

|---|---|---|

| 1 | VBUS(USB电源) | 红 |

| 2 | D+(正差分信号) | 白 |

| 3 | D-(负差分信号) | 绿 |

| 4 | GND(USB地) | 黑 |

| 外层 | 屏蔽层 | - |

5.5 例题

- 下面关于通用串行总线USB的描述,不正确的是(D)。

A. USB接口为外设提供电源

B. USB设备可以起集线器作用

C. 可同时连接127台输入/输出设备

D. 通用串行总线不需要软件控制就能正常工作

- 在嵌入式系统设计中,用来进行系统初始代码调试的接口称为(D)。

A. PCI接口

B. USB接口

C. 网络接口

D. JTAG接口

6 SPI接口基本原理与结构

- SPI接口简介

- SPI接口基本原理

- SPI接口工作模式

6.1 SPI接口简介

SPI(Serial Peripheral Interface,串行外围设备接口)是由Motorola公司开发的一个低成本、易使用的接口,主要用在微处理器(MCU)和外围设备芯片之间进行连接。

- SPI接口可以用来连接存储器、AD转换器、DA转换器、实时时钟日历、LCD驱动器、传感器、音频芯片,其他处理器等。

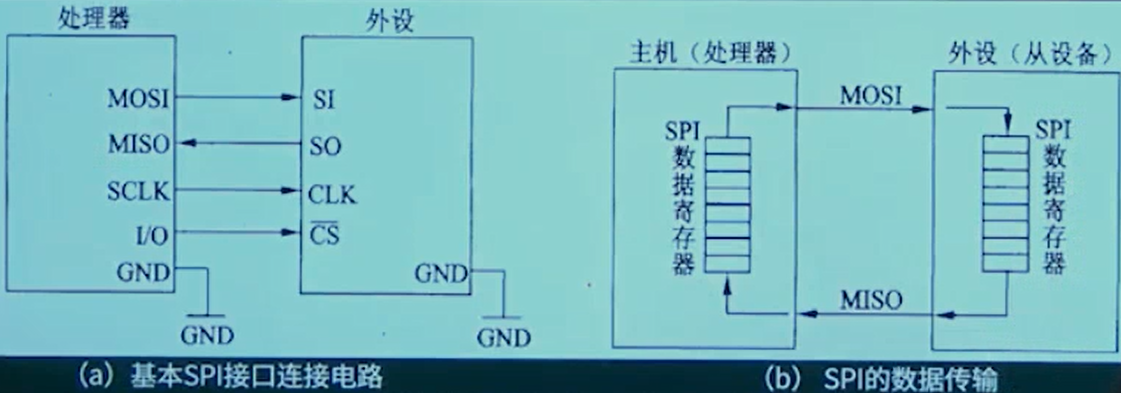

SPI是一个4线接口,主要使用4个信号。

- 主机输出/从机输入(MOSI)

- 主机输入/从机输出(MISO)

- 串行SCLK或SCK

- 外设片选( $\overline{\text{CS}}$ )

- 有些处理器有SPI接口专用的芯片选择,称为从机选择( $\overline{\text{SS}}$ )

MOSI信号由主机产生,从机接收。

- 在有些芯片上,MOSI只被简单的标为串行输入(SI),或者串行数据输入(SDI)。

MISO信号由主机产生,不过还是在主机的控制下产生的。

- 在一些芯片上,MISO有时被称为串行输出(SO)或串行数据输出(SDO)。

外设片选信号:通常只是由主机的备用I/O引脚产生的。

与标准的串行接口不同,SPI是一个同步协议接口,所有的传输都参照一个共同的时钟,这个同步时钟信号由主机(处理器)产生,接收数据的外设(从设备)使用时钟来对串行比特流的接收进行同步化。

- 可以将多个具有SPI接口的芯片连到主机的同一个SPI接口上,主机通过控制从设备的片选输入引脚来选择接收数据的从设备。

6.2 SPI接口基本原理

如图所示,微处理器通过SPI接口与外设进行连接。

- 主机和外设都包含一个串行移位寄存器,主机写入一个字节到它的SPI串行寄存器,SPI寄存器通过MOSI信号线将字节传送给外设。

- 外设也可以将自己移位寄存器中的内容通过MISO信号线传送到主机。主机和外设的两个移位寄存器中的内容被互相交换。

- 外设的写操作和读操作是同步完成的,因此SPI成为一个很有效的协议。

如果只是进行写操作,主机只需忽略收到的字节。

如果主机要读取外设的一个字节,就必须发送一个空字节来触发从机的数据传输。

当主机发送一个连续的数据流时,有些外设能进行多字节传输。

- 如多数具有SPI接口的存储器芯片都以这种方式工作。在这种传输方式下,SPI外设的芯片选择端必须在整个传输过程中保持低电平。

- 如,存储器芯片会希望在一个“写”命令之后紧接着收到的是4个地址字节(起始地址),这样后面接收到的数据就可以存储到该地址。

其他外设只需要一个单字节(比如一个发给AD转换器的命令),有些甚至还支持菊花链连接,如图所示。

- 主机处理器从其SPI接口发送3个字节的数据

- 第1个字节发送给外设A,当第2个字节发送给外设A的时候,第1个字节已移出了A,而传送给了B

- 同样,主机想要从外设A读取一个结果,它必须要再发送一个3字节(空字节)的序列,这样就可以把A中的数据移到B中,然后再移到C中,最后送回到主机。在这个过程中,主机还依次从B和C接收到字节。

注意,菊花链连接不一定适用于所有的SPI设备,特别是要求多字节传输的(比如存储器芯片)设备。有的外设西片不支持菊花链连接。

6.3 SPI接口工作模式

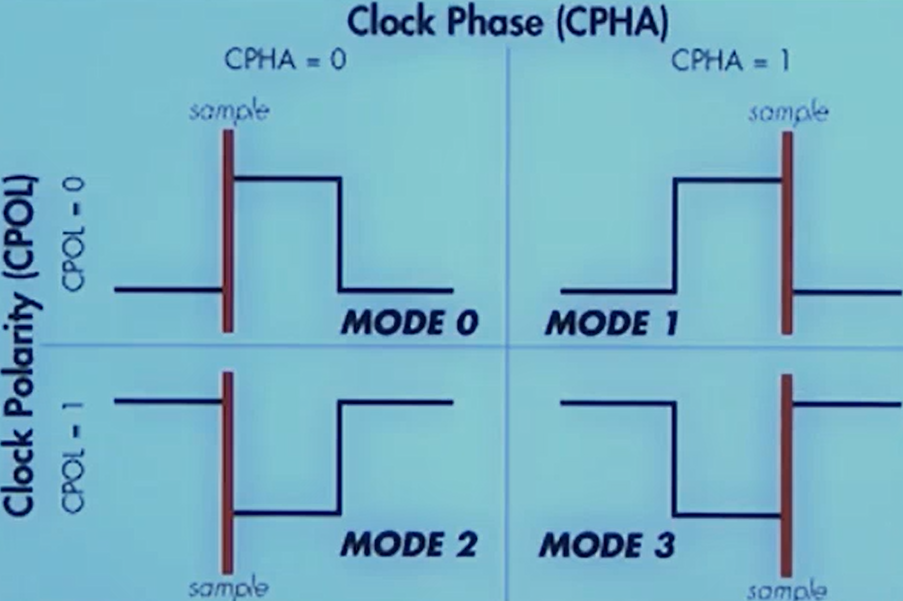

根据时钟极性和时钟相位的不同,SPI有4种工作模式。

- 时钟极性有高电平、低电平两种

- 时钟相位有两个:时钟相位0和时钟相位1

时钟极性(CPOL:Clock Polarity)。

- 时钟极性为低电平时:空闲时时钟(SCK)处于低电平,传输时跳转到高电平

- 时钟极性为高电平时:空闲时时钟(SCK)处于高电平,传输时跳转到低电平

时钟相位(CPHA:Clock Phase)。

- 当CPHA为0时,时钟周期的前一边缘采集数据

- 当CPHA为1时,时钟周期的后一边缘采集数据

四种工作模式下的SCLK表现如下。

- 红线表示采集数据,下面的一个例子是S3C2440上面SPI控制器的总线范例。

6.4 例题

- 以下四种串行总线中,一组总线上不能挂连多个器件的是(A)。

A. RS232

B. RS485

C. $I^2C$

D. SPI

7 IIC接口基本原理与结构

- IIC接口简介

- IIC总线的数据传送

- IIC总线工作原理

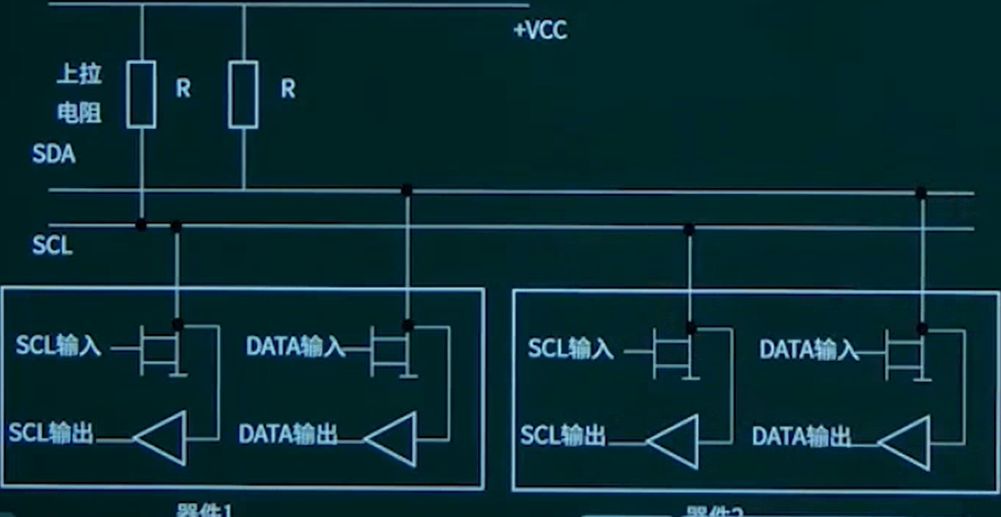

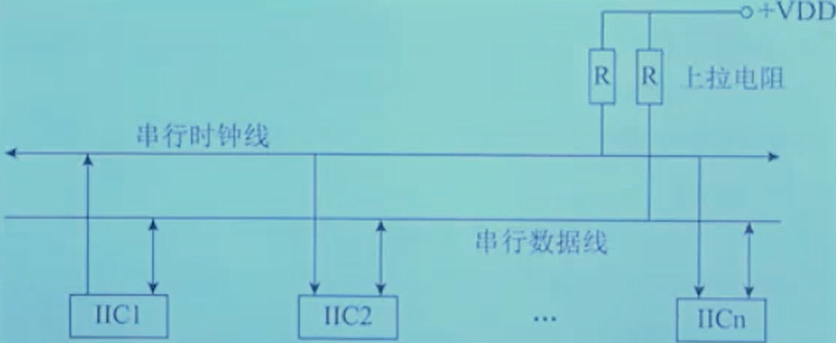

IIC Bus(Inter Integrated Circuit BUS,内部集成电路总线)是由Philips公司推出的二线制串行扩展总线,用于连接微控制器及其外围设备。

- IIC总线是具备总线仲裁和高低速设备同步等功能的高性能多主机总线

- 直接用导线连接设备,通信时无需片选信号

- IIC总线的协议层包括物理层和数据链路层。物理层有两根信号线,在链路层每个连接到IIC总线上的设备都有唯一的地址

7.1 IIC接口简介

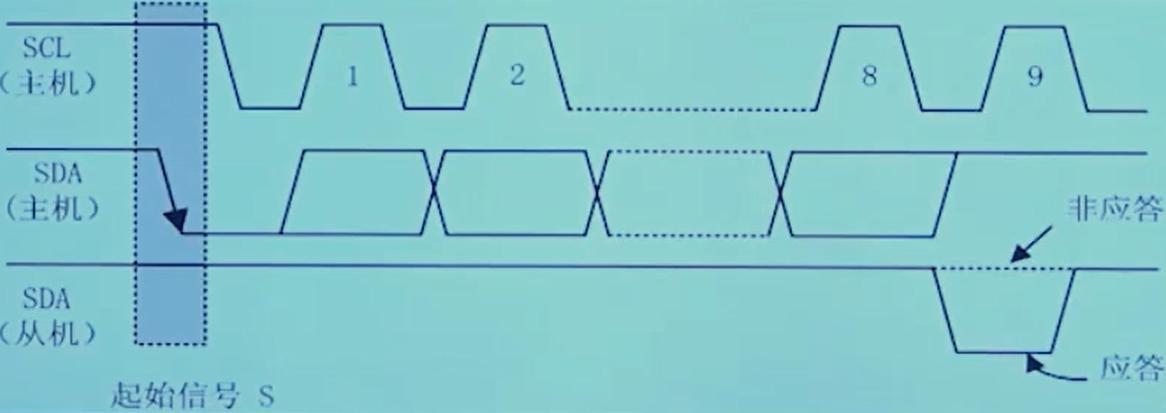

在IIC总线上,物理层只需要两条线一串行数数据SDA线、串行时钟SCL线,它们用于总线上器件之间的信息传递。

- SDA和SCL都是双向的

- 每个器件都有一个唯一的地址以供识别,而且各器件都可以作为一个发送器或接收器(由器件的功能决定的)。

7.2 操作模式

IIC总线有4中操作模式。

- 主发送模式

- 主接收模式

- 从发送模式

- 从接收模式

7.3 启动信号

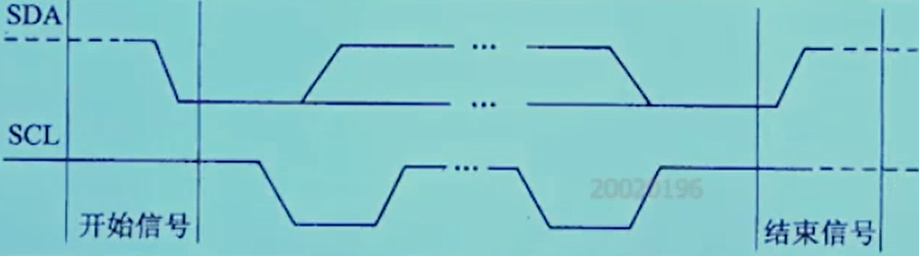

IIC总线的启动信号。

- 当IIC接口处于从模式时,要想数据传输,必须检测SDA线上的启动信号,启动信号由主器件产生

- 在SCL信号为高时,SDA产生一个由高变低的电平变化,即产生一个启动信号

- 当IIC总线上产生了启动信号后,那么这条总线就被发出启动信号的主器件占用了,变成”忙“状态

7.4 读写数据

主器件产生一个启动信号后,会立即送出一个从地址,用来通知将与它进行数据通信的从器件。

- 1个字节的地址包括7位的地址信息和1位的传输方向指示位(R/W)

- 如果第7位为“0”,表示主机发送数据(W),即进行一个写操作

- 如果“1”,表示主机接收数据(R),即进行一个读操作

7.5 数据传输格式

数据传输格式。

- SDA线上传输的每个字节长度都是8位,每次传输中字节的数量是没有限制的。

- 在起始条件后面的第一个字节是地址域,之后每个传输的字节后面都有一个应答(ACK)位(即一帧共有9位)

- 传输中串行数据的MSB(字节的高位)首先发送

7.6 应答信号

应答信号。

- 为了完成1个字节的传输操作,接收器应该在接收完1个字节之后发送ACK位到发送器,告诉发送器,已经收到了这个字节。

- ACK脉冲信号在SCL线上第9个时钟处发出(前面8个时钟完成1个字节的数据传输,SCL上的时钟都是由主器件产生的)。

- 当发送器要接收ACK脉冲时,应该释放SDA信号线,即将SDA置高。

- 接收器在接收完前面的8位数据后,将SDA拉低。

- 发送器探测到SDA为低,就认为接收器成功接收了前面的8位数据。

7.7 IIC总线工作原理

总线竞争的仲裁。

- IIC总线上可以挂接有多个器件,有时会发生两个或多个主器件同时想占用总线的情况

- IIC总线具有多主控制能力可对发生在SDA线上的总线竞争进行仲裁

- 仲裁原则:当多个主器件同时想占用总线时,如果某个器件发送高电平,而另一个主器件发送低电平,则发送电平与此时SDA总线电平不符的那个器件将自动关闭其输出级

总线竞争的仲裁在两个层次上进行的。

- 首先是地址位的比较,如果主器件寻址同一个从器件,则进入数据位的比较,从而确保了竞争仲裁的可靠性

- 由于是利用IIC总线上的信息进行仲裁,不会造成信息的丢失

IIC总线的数据传输过程。

- 开始:主设备产生启动信号,表明数据传输开始。

- 地址:主设备发送地址信息,包含7位的从设备地址和1位的数据方位指示位(读或写位,表示数据流的方向)。

- 数据:数据指示位,数据在主设备和从设备之间进行传输。数据一般以8位传输,MSB先传;具体能传输多少量的数据并没有限制。接收器产生1位的ACK(应答信号)表明收到了每个字节。传输过程可以被中止和重新开始。

- 停止:注射别产生停止信号,结束数据传输。

7.8 例题

- 关于IIC总线,下列说法错误的是(B)。

A. IIC总线有4种操作模式:主发送模式、主接收模式、从发送模式和从接收模式

B. 传输中串行数据的LSB首先发送

C. IIC总线的数据传输过程包括了开始、地址、数据和停止信号的产生

D. IIC总线上,只需要两条线——串行数据SDA线、串行时钟SCL线,它们用于总线上器件之间的信息传递,并且都是双向的

- IIC总线协议包含物理层和数据链路层,下图是常见的多个IIC设备接口示意图,下面描述不正确的是()。

A. 在物理层,IIC使用两条信号线,一条是串行数据线,一条是串行时钟线

B. 在数据链路层,每个IIC设备不用具有唯一的设备地址

C. 在IIC构成系统中,可以多主系统,但任一时刻只能有一个主IIC设备

D. IIC具有总线仲裁功能

8 网络接口

- 以太网接口基本原理与结构

- CAN总线接口基本原理与结构

- 无线以太网基本原理与结构

- 1394接口基本原理与结构

8.1 以太网接口基本原理与结构

- 以太网基础知识

- 嵌入式以太网接口的实现方法

- 网络编程接口

8.2 以太网基础知识

以太网(Ethernet)是目前应用最广泛的局域网通讯方式,同时也是一种协议。

以太网协议定义了一系列软件和硬件标准,从而将不同的设备连接在一起。

嵌入式系统通常使用的以太网协议是IEEE802.3协议。

- 以太网接口电路主要由媒质接入控制MAC控制器和物理层接口(Physical Layer,PHY)两大部分构成

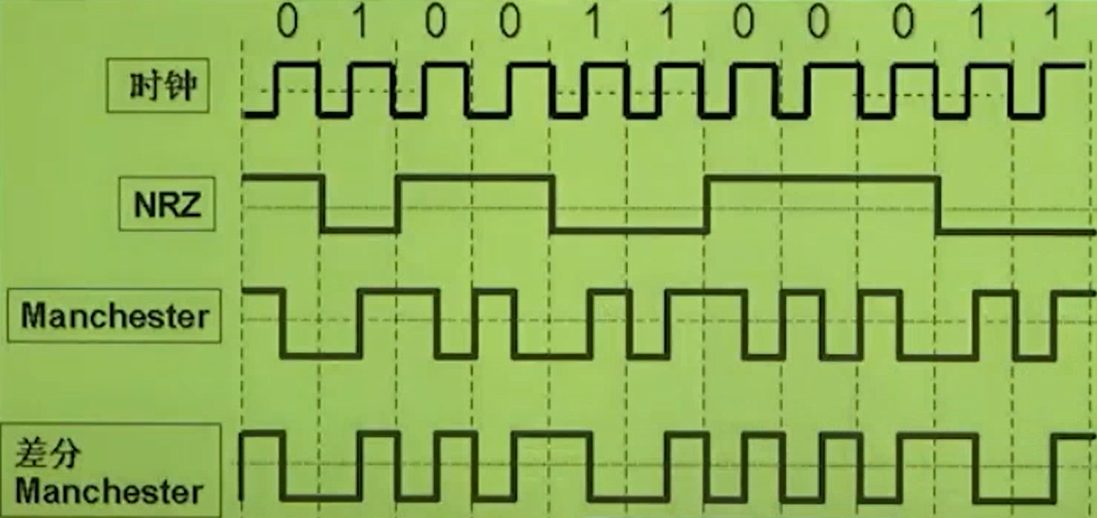

8.3 传输编码

在802.3版本的标准中,没有采用直接的二进制编码(即用0v表示“0”,用5v表示“1”),而是采用。

- 曼彻斯特编码(Manchester Encoding)

- 差分曼彻斯特编码(Differential Manchester Encoding)

曼彻斯特编码的规律。

- 每位中间有一个电平跳变,从高到低的跳变表示“0”,从低到高的跳变表示”1“。

差分曼彻斯特编码的规律。

- 每位的中间有一个电平跳变,但不用这个跳变来表示数据,而是利用每个码元开始有无跳变来表示“0”或“1”,有跳变表示“0”,无跳变表示“1”(保持性)。

曼彻斯特编码和差分曼彻斯特编码相比,前者编码简单,后者能提供更好的噪声抑制性能。

- 在802.3系统中,采用曼彻斯特编码,其高电平为+0.85v,低电平信号为-0.85v,这样指令信号电压仍然是0v。

8.4 802.3Mac层的帧

802.3 Mac层的以太网的物理传输帧如表所示。

| PR | SD | DA | SA | TYPE | DATA | PAD | FCS |

|---|---|---|---|---|---|---|---|

| 56位 | 8位 | 48位 | 48位 | 16位 | 不超过1500字节 | 可选 | 32位 |

- PR:同步位,用于收发双方的时钟同步,同时也指明了传输的速率,是56位的二进制数101010101010…,最后2位是10。

- SD:分隔位,表示下面跟着的是真正的数据而不是同步时钟,为8位的10101011。

- DA:目的地址,以太网的地址为48位二进制地址,表明该帧传输给哪个网卡。如果为FFFFFFFFFFFF,是广播地址。广播地址的数据可以被任何网卡接收到。

- SA:源地址,48位,表明该帧的数据是哪个网卡发的,即发送端的网卡地址,是6个字节。

- TYPE:类型字段,表明该帧的数据是什么类型的数据,不同协议的类型字段不同。如:0800H表示数据为IP包,0806H表示数据为ARP包,814CH是SNMP包,8137H为IPX/SPX包。

- DATA:数据段,该段数据不能超过1500B,以太网规定整个传输包的最大长度不能超过1514B(14B为DA,SA,TYPE)。

- PAD:填充位。以太网帧传输的数据包最小不能小于60B,(除去DA、SA、TYPE的14B),还必须传输46B的数据,当数据段的数据不足46B时,后面通常是补0(也可以补其他值)。

- FCS:32位数据校验位。32位的CRC校验,该校验由网卡自动计算,自动生成,自动校验,自动在数据段后面填入。不需要软件管理。

PR、SD、PAD、FCS数据段是网卡(包括物理层和Mac层的处理)层自动产生的,剩下的DA、SA、TYPE、DATA4个段的内容由上层软件控制。

8.5 以太网数据传输的特点

以太网数据传输的特点。

- 所有数据位的传输由低位开始,传输的位流用曼彻斯特编码。

- 以太网是基于冲突检测的总线复用方法,冲突退避算法是由硬件自动执行。

- 以太网传输的数据段的长度,DA + SA + TYPE + DATA + PAD最小为60B,最大为1514B。

- 通常的以太网卡可以接收3种地址的数据:广播地址、多播地址(或者叫组播地址,在嵌入式系统中很少用到)、自己的地址。但有时,用于网络分析和监控,网卡也可以设置为接收任何数据包。

- 任何两个网卡的物理地址都是不一样的,是世界上唯一的,网卡地址由专门机构分配。不同厂家使用不同地址段,同一厂家的任何两个网卡的地址也是唯一的。根据网卡的地址段(网卡地址的前3个字节)可以知道网卡的生产厂家。

8.6 以太网接口实现的方法

嵌入式处理器 + 网卡芯片。

- 把以太网芯片连接到嵌入式处理器的总线上。

- 通用性强,对嵌入式处理器没有特殊要求,不受处理器的限制,但是,嵌入式处理器和网络数据交换通过外部总线(通常是并行总线)交换数据,速度慢,可靠性不高,电路板走线复杂。

- 目前常见的以太网接口芯片,如CS8900、RTL8019/8029/8039、DM9008及DWL650无线网卡等。

带有以太网接口的嵌入式处理器。

- 常有以太网接口的嵌入式处理器通常是面向网络应用而设计的,要求嵌入式处理器有通用的网络接口(比如:MII接口)。

- 处理器和网络数据交换通过内部总线,速度快。

8.7 网络编程接口

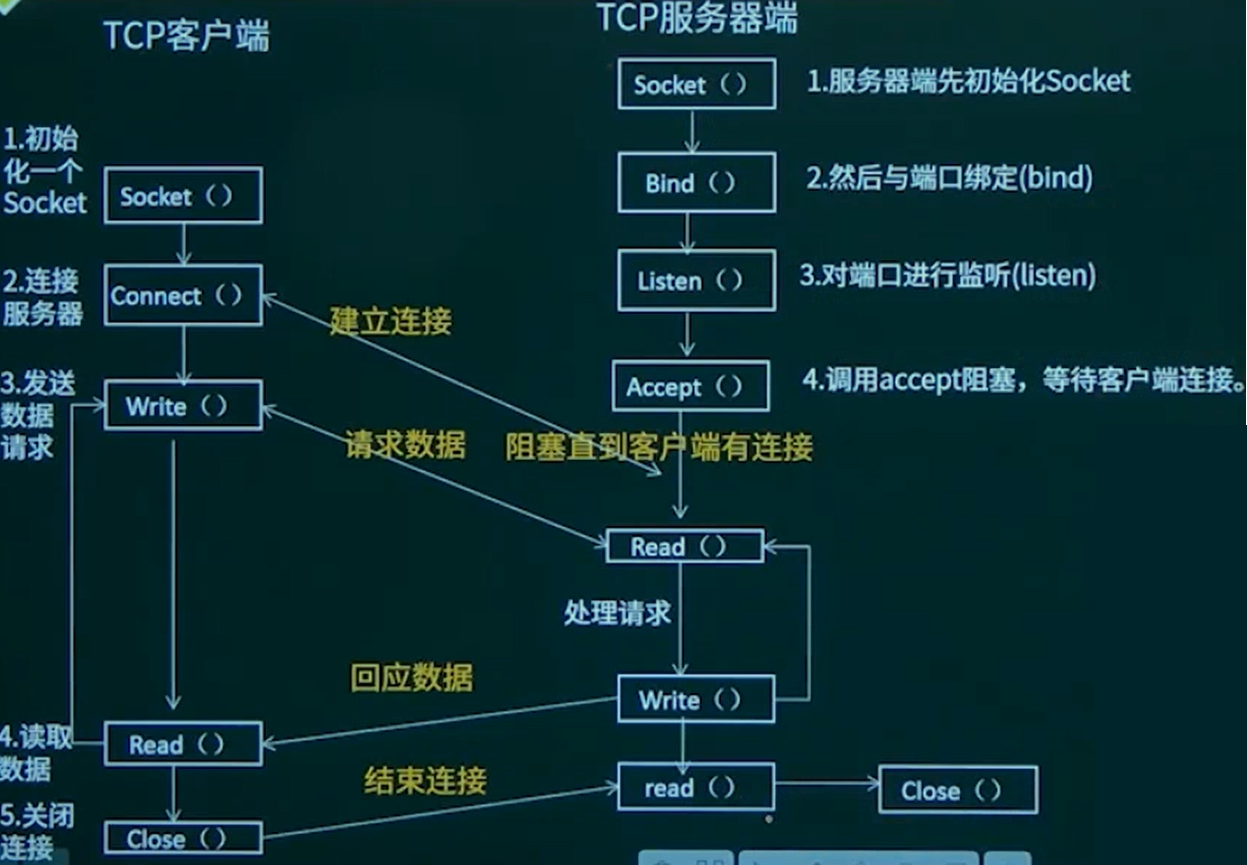

BSD套接字(BSD Sockets)是使用的最广泛的网络程序编程方法。

- 主要用于应用程序的编写,用于网络上主机与主机之间的相互通信。

- 很多操作系统都支持BSD套接字编程。例如,UNIX、Linux、VxWorks、Windows的Winsock基本上是来自BSD Sockets。

套接字(Sockets)分为Stream Sockets和Data Sockets。

- Stream Sockets是可靠性的双向数据传输,对应使用TCP协议传输数据

- Data Sockets是不可靠连接,对应使用UDP协议传输数据

8.8 例题

略

9 CAN总线接口基本原理与结构

- CAN总线概述

- 在嵌入式处理器上扩展CAN总线接口

9.1 CAN总线概述

CAN(Controller Area Netword,控制器局域网)是德国Bosch公司于1983年为汽车应用而开发的,它是一种现场总线(FieldBus),能有效支持分布式控制和实时控制的串行通信网络。

- 1993年11月,ISO正式颁布了控制器局域网CAN国际标准(ISO11898)。

CAN总线是一种多主方式的串行通信总线。

- 理想的由CAN总线构成的单一网络中,是可以挂接任意多个节点,实际应用中节点数目受网络硬件的电气特性所限制。例如:当使用Philips P82C250作为CAN收发器时,同一网络中允许挂接110个节点。

- CAN总线具有很高的实时性能,已经在汽车工业、航空工业、工业控制、安全防护等领域中得到了广泛应用。

CAN总线的通信介质可采用双绞线、同轴电缆和光导纤维,最常用的是双绞线。

- 通信距离与波特率有关,最大通信距离可达10km,最大通信波特率可达1Mbps。

- CAN总线仲裁采用11位标识和非破坏性位仲裁总线结构机制,可以确定数据块的优先级,保证在网络节点冲突时最高优先级节点不需要冲突等待。

- CAN总线采用了多主竞争式总线结构,具有多主站运行和分散仲裁的串行总线以及广播通信的特点。

- CAN总线上任一节点可在任一时刻主动向网络上其他节点发送信息而不分主次,因此可在各节点之间实现自由通信。

CAN总线信号使用差分电压传送。

- 两条信号线被称为CAN_H和CAN_L,静态时均是2.5v左右,此时状态表示为逻辑1,也可以叫作“隐形”。

- 采用CAN_H比CAN_L高表示逻辑0,称为“显性”,通常电压值为CAN_H = 3.5v和CAN_L = 1.5v。

- 当“显性”位和“隐性”位同时发送的时候,最后总线数值降为“显性”。

- 这种特性为CAN总线的仲裁奠定了基础。

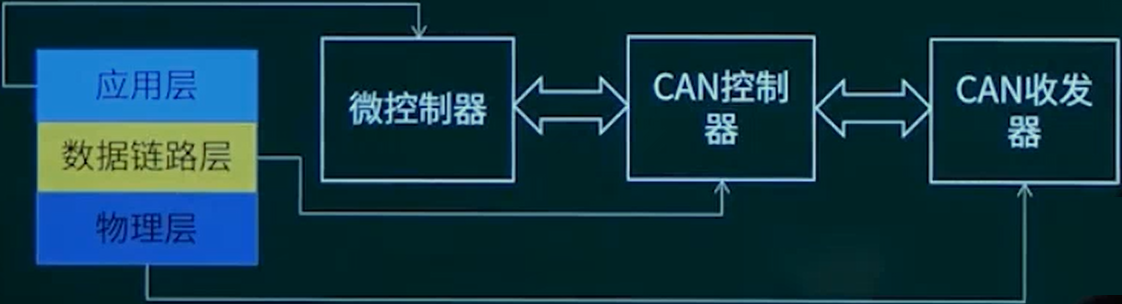

9.2 CAN总线接口

一些面向工业控制的嵌入式处理器集成了一个或者多个CAN总线控制器。

- 例如:Phillips公司的LPC2194和LPC2294(ARM7TDMI内核)带有4个CAN总线控制器。

- CAN总线控制器主要是完成时序控制逻辑转换等工作,要在电气特性上满足CAN总线标准,还需要一个CAN总线的物理层芯片,用它来实现TTL电平到CAN总线电平特性的转换,即CAN收发器。

实际上,多数嵌入式处理器都不带CAN总线控制器。

- 通常的解决方案是在嵌入式处理器的外部总线上扩展CAN总线接口芯片。

- 例如:Phillips公司的SJA1000 CAN总线接口芯片,Microchip公司的MCP251x系列(MCP2510和MCP2515)CAN总线接口芯片,这两种芯片都支持CAN2.0B标准。

- SJA 1000的总线采用的是地址线和数据线复用的方式,多数嵌入式处理器采用SJA 1000扩展CAN总线较为复杂。

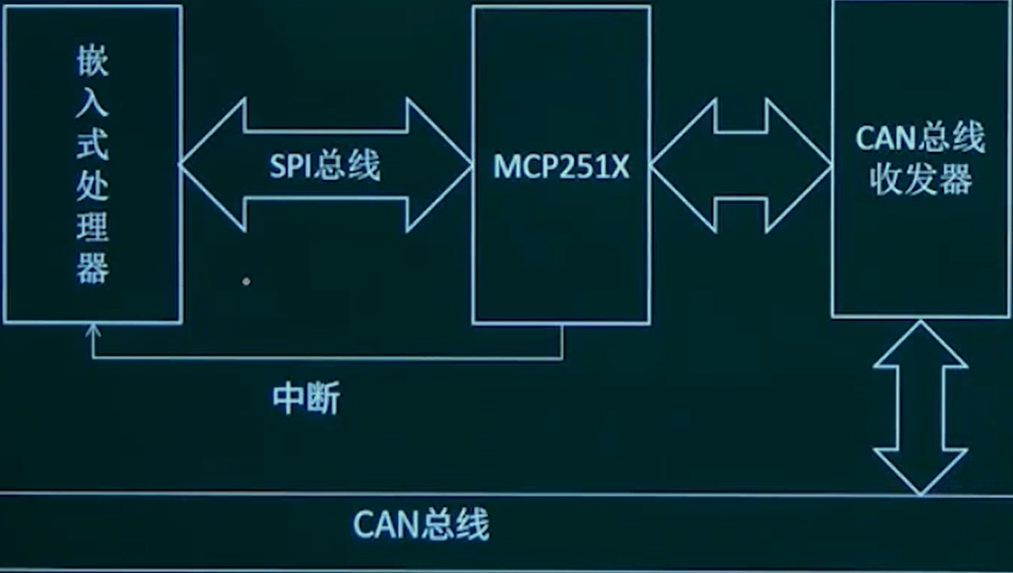

9.3 嵌入式处理器上扩展CAN总线接口

MCP2510是由Microchip公司生产的CAN协议控制器,完全支持CAN总线V2.0A/B技术规范。

- 0~8字节的有效数据长度,支持远程帧

- 最大1Mb/s的可编程波特率

- 两个支持过滤波器(Filter,Mask)的接收缓冲区,三个发送缓冲区

- 支持回环(Loop Back)模式,便于测试

- SPI高速串行总线,最大5MHz

- 3v到5.5v供电

大多数嵌入式处理器都有SPI总线控制器,MCP2510可以3v到5.5v供电,能够直接和3.3v I/O口的嵌入式处理器连接,电路原理图如图所示。

MCP2510使用3.3v电压供电,可以直接和三星S3C44B0X处理器通过SPI总线连接。相关的资源如下。

- 使用一个扩展的I/O口(EXIO2)作为片选信号,电平有效。

- 用S3C2410A的外部中断6(EXINT6)作为中断管脚,低电平有效。

- 16MHz晶体作为输入时钟,MCP2510内部有晶振电路,用晶体可以直接起振使用TJA1050作为CAN总线收发器。

CAN总线收发器TJA1050必须使用5v供电。MCP2510和TJA1050连接的两个信号都是单向的信号。需要满足I/O口的电气特性。

- 从MCP2510输出的TXCAN信号是否满足TJA1050的输入电平。TJA1050位5v供电时,输入高电平 $V_{ih}$ 的范围是2~5.3v。而3.3v供电的MCP2510输出TXCAN信号高电平 $V_{oh}$ 最小值为2.6v,可以满足要求。

- 从TJA1050输出的RXD信号是否满足MCP2510的输入电平。3.3v供电的MCP2510输入信号RXCAN高电平范围 $V_{ih}$ :2~4.3v,无法满足5v逻辑的TJA1050输出电平,电阻分压实现单向电平转换。

分压电阻值的选择,需要考虑2个问题。

- TJA1050输出信号的驱动能力(输出电流 $\leq 15mA$ )

- MCP2510的RXCAN管脚的输入阻抗(输入电流 $\leq 5μA$ )

10 无线以太网基本原理与结构

- WLAN简介

- WLAN标准

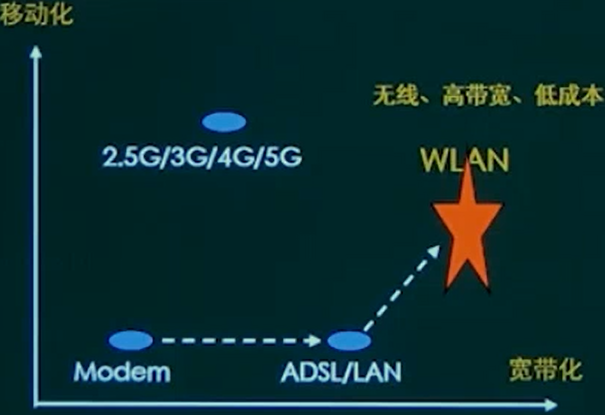

10.1 WLAN简介

WLAN(Wireless Local Area Network,无线局域网)是利用无线通信技术在一定局部范围内建立的,是计算机网络与无线通信技术相结合的产物,以无线多址通道作为传输媒介,提供有线局域网的功能。

传输介质。

- 红外线IR

- 射频RF波段

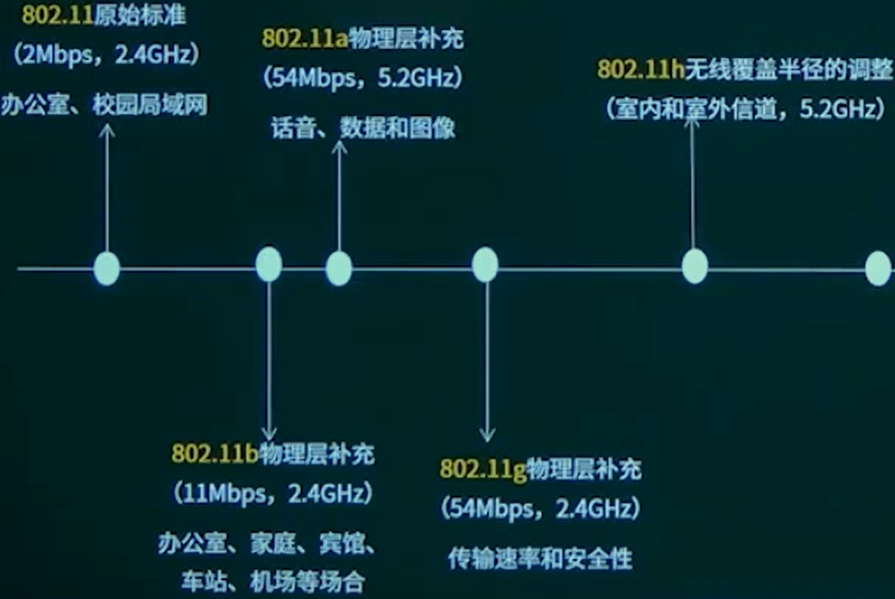

10.2 WLAN标准

WLAN的标准:主要是针对物理层和媒质访问控制层(MAC层)。

- 涉及到所有使用的无线频率范围、控制接口通信协议等技术规范与技术标准。

11 IEEE 1394接口基本原理与结构

- IEEE 1394简介

- IEEE 1394的特点

- IEEE 1394的协议结构

11.1 IEEE 1394简介

IEEE 1394是Apple公司率先提出的一种高品质、高传输速率的串行总线技术,1995年被IEEE认定为串行工业总线标准。

- 1394作为一种标准总线,可以在不同的工业设备之间架起一座沟通的桥梁

- 在一条总线上可以接入63个设备

- 实时多媒体领域,大容量存储以及打印机、扫描仪上等等

- IEEE 1394规范仅支持64位固定解址模式

11.2 IEEE 1394的特点

支持多种总线速度,适应不同应用要求。

- IEEE 1394a:100Mb/s、200Mb/s、400Mb/s

- IEEE 1394b:800Mb/s、1600Mb/s、3200Mb/s

支持热插拔。

- 设备的资源均由总线控制器自动分配

- 总线控制器会自动重新配置好设备

接口有两种类型。

- 6针的六角形接口和4针的小型四角形接口

- 6针的六角形接口可向所连接的设备供电,而4针的四角形接口则不能

支持同步和异步两种传输方式。

- 设备可以根据需要动态地选择传输方式,总线自动完成带宽分配

- 要求实时传输并对数据的完整性要去不严格的场合,可采用同步传输方式

- 对数据完整性要求较高的场合,采用异步传输方式更好

支持点到点通信模式,IEEE 1394是多主总线。

- 每个设备均可以获取总线的控制权,与其他设备进行通信。

两种传输方式:Backplane模式和Cable模式。

- Backplane模式最小的速率也比USB1.1最高速率高,分别为12.5Mbps/s、25Mbps/s、50Mbps/s,可以用于多数的高带宽应用。

- Cable模式是速度非常快的模式,分为100Mbps/s、200Mbps/s和400Mbps/s几种,在200Mbps/s下可以传输不经压缩的高质量数据电影。

遵循ANSI IEEE 1212控制及状态寄存器(CSR)标准,定义了64位的地址空间。

- 可寻址1024条总线的63个节点,每个节点包含256TB的内存空间

支持较远距离的传输。

- 普通线缆:2个设备之间的最大距离可达4.5m(高级线缆可达15m)

- 玻璃光缆或5类双绞线:设备间距离可达100m以上。

支持公平仲裁原则,为每一种传输方式保证足够的传输带宽。

- 支持错误检测和处理。

六线电缆具有电源线,可传输8~40v的直流电压。

- 2对双绞线:信号传递

- 1对双绞线:供应电源

11.3 IEEE 1394的协议结构

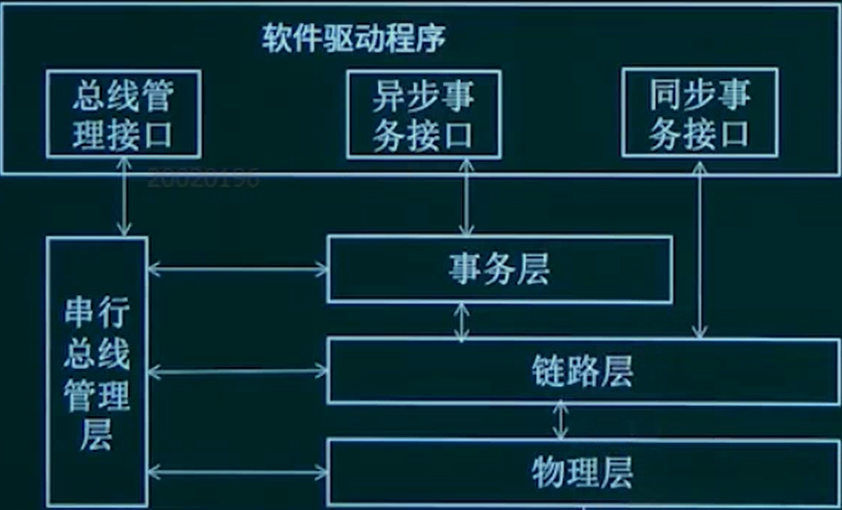

IEEE 1394的协议栈由3层组成:物理层、链路层和事务层,另外还有一个管理层。

- 物理层和链路层由硬件构成,通常集成在同一块芯片上

- 事务层主要由软件实现

物理层提供IEEE1394的电气和机械接口,功能是重组字节流并将它们发送到目的节点上去。

- 物理层为链路层提供服务

- 解析字节流并发送数据包给链路层

链路层提供了给事务层确认的数据服务,包括:寻址、数据组帧和数据校验。

- 提供直接面向应用的服务

- 支持同步和异步传输模式

- 链路层的底层提供了仲裁机制

11.4 例题

- IEEE 1394具有(D)位地址空间,IEEE 1394的通信协议具有三个协议包,不包括(B)。

(1)

A. 8

B. 16

C. 32

D. 64

(2)

A. 事物层

B. 表示层

C. 链路层

D. 物理层

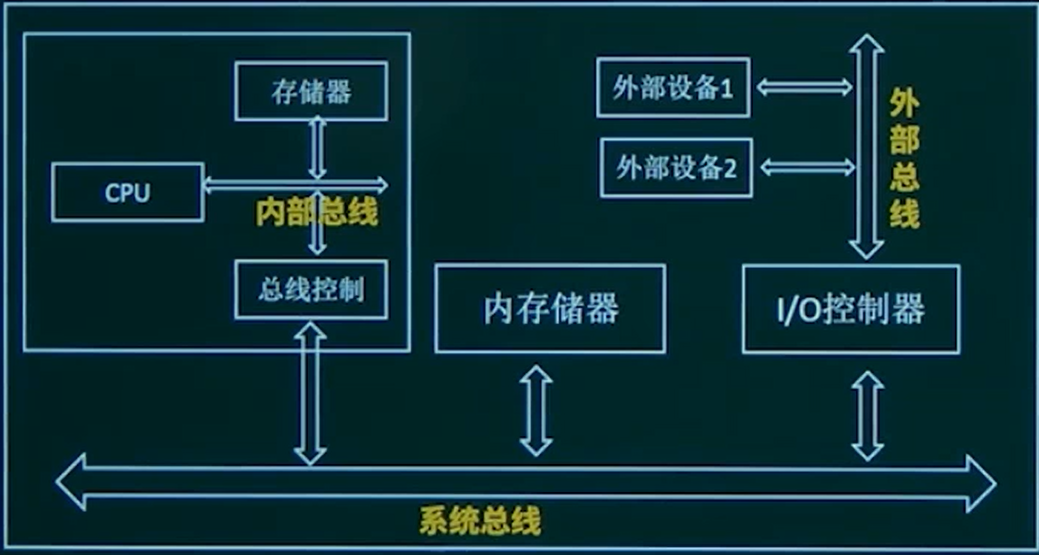

12 总线分类

| 总线分类 | 说明 | 常用总线 |

|---|---|---|

| 内部总线 | 内部总线是微处理机内部各外围芯片与处理器之间的总线,用于芯片一级的互连 | IIC总线、SPI总线、SCI总线等 |

| 系统总线 | 系统总线是微机中各插件板与系统板之间的总线,用于插件板一级的互连 | ISA总线、EISA总线、VESA总线、PCI总线等 |

| 外部总线 | 外部总线则是微机和外部设备之间的总线,微机作为一种设备,通过该总线和其他设备进行信息与数据交换,它用于设备一级的互连 | RS232、RS485、USB总线、IEEE1394总线等 |

12.1 例题

- 以下关于嵌入式系统总线的描述中,不正确的是(C)。

A. 异步通信时数据是一帧一帧传送的,没帧数据的传送靠起始位来同步

B. SPI、IIC、UART都属于串行通信方式

C. 同步通信方式是字符同步,且在字符与字符之间的时序仍然是同步的

D. RS232、RS485、USB、IEEE1394总线都属于外部总线

- 不属于系统总线的是(C)。

A. ISA

B. EISA

C. SCSI

D. PCI

2.2 串行通信模式

2.2.1 单工

串行数据传送有3种基本的通信模式:单工、半双工、全双工通信。

单工通信:数据仅能从设备A到设备B进行单一方向的传输。如遥控、遥测等。

第十四章——嵌入式系统总线和通讯接口

前言:

计算机第十四章节主要知识点。

1 知识点介绍

- 串行接口基本原理与结构

- 并行接口基本原理与结构

- PCI接口基本原理与结构

- USB接口基本原理与结构

- SPI接口基本原理与结构

- IIC接口基本原理与结构

- 网络接口基本原理与结构

- 总线分类

2 串行接口基本原理与结构

- 串行通信概述

- RS-232C串行接口

- RS-422串行通信接口

- RS-485串行总线接口

2.1 串行通信概述

串行通信:数据是一位一位地进行传输的,在传输中每一位数据都占据一个固定的时间长度。

优点。

- 传输线少、成本低

- 特别适合远距离传送

缺点。

- 速度慢

2.2 串行通信模式

2.2.1 单工

串行数据传送有3种基本的通信模式:单工、半双工、全双工通信。

单工通信:数据仅能从设备A到设备B进行单一方向的传输。如遥控、遥测等。

2.2.2 半双工

半双工通信:数据可以从设备A到设备B进行传输,也可以从设备B到设备A进行传输,但不能在同一时刻进行双向传输。如:对讲机。

2.2.3 全双工

全双工通信:数据可以在同一时刻从设备A传输到设备B,或从设备B传输到设备A,即可以同时双向传输。如电话。

2.2.4 串行通信异步

串行通信在信息格式上可以分为:异步通信和同步通信方式。

异步通信方式。

- 是指通信的发送与接收设备使用各自的时钟,控制数据的发送和接收过程。

- 为使双方的收发协调,要求发送和接收设备的时钟尽可能一致。

异步通信方式。

- 数据是一帧一帧传送的,没帧数据包含有起始位(“0”)、数据位、奇偶校验位和停止位(“1”),每帧数据的传送靠起始位来同步。

- 一帧数据的各位代码间的时间间隔是固定的,而相邻两帧的数据其时间间隔是不固定的。

- 在异步通信的数据传送中,传输线上允许空字符。

字符格式。

- 异步通信对字符格式、波特率、校验位有确定的要求。

字符格式。

- 每个字符传送时,必须前面加一位起始位,后面加上1、1.5或2位停止位。

- 例如ASCII码传送时,一帧数据的组成是:前面1个起始位,接着7位ASCII编码,再接着一位奇偶校验位,最后一位停止位,共10位。

2.2.5 波特率和校验位

波特率。

- 传送数据位的速率称为波特率,用位/秒(bit/s)来表示,称之为波特。

- 例如,数据传送的速率为120字符/秒,每帧包括10个数据位,则传送波特率为: $10 \times 120 = 1200b/s = 1200波特$

- 异步通信的波特率的数值通常为:150、300、600、1200、2400、4800、9600、14400、28800等,数值成倍数变化。

校验位。

- 偶校验就是要使字符加上校验位有偶数个“1”。

- 奇校验就是要使字符加上校验位有奇数个“1”。

- 例如数据“00010011”,共有奇数个“1”,偶校验时,则校验位就置为“1”,奇校验时,则校验位就置为“0”。

2.2.6 串行异步特点

异步通信的特点。

- 不要求收发双方时钟的严格一致,实现容易,设备开销较小。

- 但每个字符要附加2~3位用于起始,各帧之间还有间隔,因此传输效率不高。实际使用率只有约80%。

2.2.7 串行通信同步

同步通信。

- 是一种比特同步通信技术,要求收发双方具有同频同相的同步时钟信号,只需在传送报文的最前面附加特定的同步字符,使收发双方建立同步,此后便在同步时钟的控制下逐位发送/接收。

- 同步传输采用字符块的方式,减少每一个字符的控制和错误检测数据位,因而可以具有较高的传输速率。

- 即将许多字符聚集成一字符块后,在每块信息之前要加上1~2个同步字符,字符块之后再加入适当的错误检测数据才传送出去。

特点。

- 数据传输速率较高。

- 但要求发送方时钟和接收方时钟保持严格同步。

2.2.8 串口同步和异步发送

2.3 RS-232C串行接口

2.3.1 接口规格

RS-232C是美国电子工业协会(EIA)制定的一种串行通信接口标准。

RS-232C接口规格。

- EIA所制定的传送电气规格如下表所示。

- RS-232C通常以±12v的电压来驱动信号线,TTL标准与RS-232C标准之间的电平转换电路通常采用集成电路芯片实现,如M2AX23等。

| 状态 | L(Low) | H(Hight) |

|---|---|---|

| 电压范围 | -25~-3v | +3v~25v |

| 负逻辑 | 1 | 0 |

2.3.2 接口信号

EIA制定的RS-232C接口与外界的相连采用25芯(DB-25)和9芯(DB-9)D型插接件,实际应用中,并不是每只引脚信号都必须用到。

2.3.3 引脚功能

RS-232C DB-9各引脚功能如下。

| 引脚号 | 符号表示 | 名称 | 说明 |

|---|---|---|---|

| 1 | CD | 载波检测 | 主要用于Modem通知计算机其处于在线状态,即Modem检测到拨号音 |

| 2 | RXD | 接收数据线 | 用于接收外部设备送来的数据 |

| 3 | TXD | 发送数据线 | 用于将计算机的数据发送给外部设备 |

| 4 | DTR | 数据终端 | 当次引脚高电平时,通知Modem可以进行数据传输,计算机已经准备好 |

| 5 | SG | 信号地 | |

| 6 | DSR | 数据设备就绪 | 此引脚为高电平时,通知计算机Modem已经准备好,可以进行数据通信 |

| 7 | RTS | 请求发送 | 此引脚由计算机来控制,用以通知Modem马上传送数据至计算机,否则Modem将收到的数据暂时放入缓冲区中 |

| 8 | CTS | 允许发送 | 此引脚由Modem控制,用以通知计算机将要传送的数据送至Modem |

| 9 | RI | 振铃提示 | Modem通知计算机有呼叫进来,是否接听呼叫由计算机决定 |

2.3.4 连接方式

RS-232C的基本连接方式。

- 计算机利用RS-232C接口进行串口通信,有简单连接和完全连接两种连接方式

- 简单连接又称三线连接,即只连接发送数据线、接收数据线和信号地,实现全双工通信

- 如果应用中还需要使用RS-232C的控制信号,则采用完全连接方式。

2.4 RS-422串行接口

RS-422标准是RS-232的改进型,是一种可单机发送多机接收的平衡传输规范,传输速率可达10Mb/s。采用差分传输方式,也称平衡传输。

- 允许在相同传输线上连接多个接收节点,最多可接10个节点,即一个主设备(Master),其余10个为从设备(Slave),从设备之间不能通信。

- 支持一点对多点的双向通信。RS-422四线接口由于采用单独的发送和接收通道,因此不必控制数据方向,各装置之间任何必须的信号交换均可以按软件方式(XON/XOFF握手)或硬件方式(一对单独的双绞线)实现。

RS-422的最大传输距离为4000英尺(约1219m),最大传输速率为10Mb/s。

- 传输速率与平衡双绞线的长度有关,只有在很短的距离下才能获得最高传输速率

- 在最大传输距离时,传输速率为100kb/s

- 一般100m长的双绞线上所能获得的最大传输速率仅为1Mb/s

RS-422需要在传输电缆的最远端连接一个电阻,要求电阻阻值约等于传输电缆的特性阻抗。

- 在短距离(300m以下)传输时可以不连接电阻。

2.5 RS-485串行接口

在RS-422的基础上,为扩展应用范围,EIA制定了RS-485标准,增加了多点、双向通信能力。

- 在通信距离为几十米至上千米时,通常采用RS-485接收器

- RS-485接收器采用平衡发送和差分接收

- 即在发送端,驱动器将TTL电平信号转换成差分信号输出,在接收端,接收器将差分信号变成TTL电平,因此具有抑制共模干扰的能力。

- 接收器能够检测低达200mv的电压,具有高的灵敏度,故数据传输距离可达千米以上。

RS-485可以采用二线与四线方式,二线制可以实现真正的多点双向通信。

- 采用四线连接时,与RS-422一样只能实现点对点的通信,即只能有一个主设备,其余为从设备。

- RS-485可以连接多达32个设备

RS-485的共模输出电压在-7~+12v之间,接收器最小输入阻抗为12kΩ。

RS-485满足所有RS-422的规范,所以RS-485的驱动器可以在RS-422网络中应用。

RS-485的最大传输速率为10Mb/s。在最大传输距离时,传输速率为100kb/s。

RS-485需要两个终端电阻,接在传输总线的两端,要求电阻阻值约等于传输电缆的特性阻抗。

- 在短距离传输(在300m以下)时可不需终端电阻。

2.6 例题

- 使用串行总线传输数据时,被传输的数据(D)。

A. 在发送设备和接收设备中都是进行串行到并行的变换

B. 在发送设备和接收设备中都是进行并行到串行的变换

C. 在发送设备中进行串行到并行的变换,接收设备中进行并行到串行的变换

D. 在发送设备中进行并行到串行的变换,接收设备中进行串行到并行的变换

3 并行接口基本原理与结构

- 并行接口分类

- 并行总线

3.1 并行接口基本概念

并行通信通常是将数据字节的各位用多条数据线同时进行传送。

- 一般用来连接打印机、扫描仪等,所以又称打印口。

特定。

- 控制简单,传输速度快

- 由于传输线较多,长距离传送时成本高且接收方的各位同时接收存在的困难。

3.2 并行接口分类

并行接口可以分为。

- SPP(标准并口)

- EPP(增强型并口)

- ECP(扩展型并口)

3.3 并行总线分类

&emsep; 并行总线分为。

- 标准并行总线

- 非标准并行总线

常用的并行标准总线:IEEE488总线和SCSI总线。

总线是一种高性能非标准的通用多用户并行总线。

3.4 并行总线IEE488

IEEE488总线。

- 又称GPIB总线(General Purpose Interface Bus,通用接口总线)

- 位并行、字节串行双向异步方式传输信号

- 总线方式连接,仪器设备直接并联于总线上,总线上最多可连接15台设备

- 最大传输距离为20m,信号传输速度一般为500kb/s,最大传输速度为1Mb/s

- 广泛应用在仪器、仪表、测控领域

3.5 并行总线SCSI和MXI

SCSI(Small Computer System Interface,小型计算机系统接口)总线。

- 速度可达5Mb/s,传输距离6m

- 传输速率很高

- 普通用作计算机的高速外设总线,如连接高速硬盘驱动器

MXI总线(Multi-system Extension Interface bus,多系统扩展接口总线)。

- 是一种高性能非标准的通用多用户并行总线

- 32位高速并行总线

- 最高速度可达23Mb/s,传输距离20m

- 用作计算机与测控机箱的互连

3.6 例题

- 串行总线与并行总线比,(C)。

A. 串行总线成本高,速度快

B. 串行总线成本高,速度慢

C. 并行总线成本高,速度快

D. 并行总线成本低,速度快

- 信息可以在两个方向上同时传输的总线属于(C)。

A. 单工总线

B. 半双工总线

C. 全双工总线

D. 单向总线

- 以下关于总线的叙述中,不正确的是(C)。

A. 并行总线适合近距离高速数据传输

B. 串行总线适合长距离数据传输

C. 单总线结构在一个总线上适合不同种类的设备,设计简单且性能很高

D. 专用总线在设计上可以与连接设备实现最佳匹配

4 PCI接口基本原理与结构

- PCI接口基本结构

4.1 PCI接口基本结构

PCI(Peripheral Component Interconnect,外围设备互连)总线是由Intel公司推出的一种局部总线,是当前用于系统扩展最流行的总线之一。

PCI总线是地址、数据多路复用的高性能32位和64位总线,是微处理器与外围控制部件、外围附加板之间的互连机构。

PCI定义了32位数据总线,并且可扩展为64位。总线速度有32MHz和66MHz两种。

- 改良的PCI系统PCI-X,数据传输速度最高可以达到64位@133MHz

- PCI总线主板插槽的体积比ISA总线插槽小,支持突发读写操作(突发数据传输),可同时支持多组外围设备

与ISA总线不同,PCI总线的地址总线与数据总线是分时复用的,支持即插即用(PNP:Plug-and-Play)、中断共享等功能。

PCI总线在数据传输时,由一个PCI设备做发起者(称为Master、Initator),而另一个PCI设备做目标(称为Slave、Target)。

- 总线上所有时序的产生与控制都由Master发起

- PCI总线在同一时刻只能供一对设备完成传输,要求有一个仲裁机构来决定谁有权拿到总线的主控权

4.1.1 例题

- 关于PCI总线,下列说法不正确的是(A)。

A. PCI总线是地址、数据多路复用的一种总线,不支持即插即用,支持中断共享功能

B. PCI定义了32位数据总线,也可扩展为64位总线

C. PCI总线在数据传输时,由一个PCI设备做发起者,而另一个PCI设备做目标

D. PCI总线要求有一个仲裁机构来决定谁有权拿到总线的主控权,所以在同一时刻只能供一对设备完成传输

- 在以下描述中PCI总线的基本概念中,正确的表述有(B)、(E)、(F)、(G)、(J)、(K)。

A. PCI总线是一个与处理器有关的高速外围总线

B. PCI总线的基本传输机制是触发传输

C. PCI设备一定是主设备

D. PCI的物理地址与其他总线一样,是由内存地址空间和I/O地址组成

E. PCI设备的地址译码不能对配置空间直接寻址

F. PCI设备识别主要是对开发商代码和设备代码进行识别

G. 访问配置空间时,PCI桥应提供IDSEL信号以选择PCI设备

H. 系统中只允许有一条PCI总线

I. PCI总线是高速串行总线

J. PCI总线有3种桥,即HOST/PCI桥,PCI/PCI桥,PCI/LEGACY桥

K. PCI桥是可以把一条总线的地址空间映射到另一条总线的地址空间

5 USB接口基本原理与结构

- USB总线的主要性能特点

- 物理接口

USB(Universal Serial Bus,通用串行总线)是由Compaq、HP、Intel、Lucent、Microsoft、NEC和Philips公司制定的连接计算机与外围设备的机外串行总线。

- 最多可连接127个设备

- 用于多种嵌入式系统设备的数据通信。如移动硬盘、PDA

5.1 热插拔

USB提供机箱外的热插拔功能,连接外设不必再打开机箱,也不必关闭主机电源,USB可智能地识别USB链上外围设备的动态插入或拆除,具有自动配置和重新配置外设的能力,连接设备方便,使用简单。

可连接多个外部设备。

- 每个USB系统中有1个主机,USB总线采用“级联”方式可连续多个外部设备。

- 每个USB设备用一个USB插头连接到上一个USB设备的USB插座上,而其本身又提供一或多个USB插座供一下一个或多个USB设备连接使用。

- 这种多重连接是通过集线器(Hub)来实现的,整个USB网络中最多可连接127个设备,支持多个设备同时操作

5.2 USB总线的主要性能特点

可同时支持不同同步传输方式和速率的设备。

- 可同时支持同步传输和异步传输两种传输方式

- 可同时支持不同速率的设备,速率最高可达几百Mb/s

- 支持主机与设备之间的多数据流和多消息流传输,且支持同步和异步传输类型

- 提供了四种不同的数据传输类型:控制传输、数据传输、中断数据传输和同步数据传输

较强的纠错能力。

- USB系统可实时地管理设备插拔

- 在USB协议中包括了传输错误管理、错误恢复等功能,同时根据不同的传输类型来处理传输错误

低成本的电缆和连接器。

- USB采用统一的4引脚插头和一根四芯的电缆传送信号和电源

- 电缆长度可达5m

总线供电。

- USB总线可以为连接在其上的设备提供5v电压/100mA电流的供电,最大可提供500mA的电流

- USB设备也可采用自供电方式,可以通过电池或其他的电力设备

- 支持节约能源的挂机和唤醒模式

5.3 USB总线的应用

5.4 USB总线物理接口

USB总线的电缆有一对标准尺寸的双绞信号线和一对标准尺寸的电源线,共4根导线。

| 连接序号 | 信号名称 | 典型连接线 |

|---|---|---|

| 1 | VBUS(USB电源) | 红 |

| 2 | D+(正差分信号) | 白 |

| 3 | D-(负差分信号) | 绿 |

| 4 | GND(USB地) | 黑 |

| 外层 | 屏蔽层 | - |

5.5 例题

- 下面关于通用串行总线USB的描述,不正确的是(D)。

A. USB接口为外设提供电源

B. USB设备可以起集线器作用

C. 可同时连接127台输入/输出设备

D. 通用串行总线不需要软件控制就能正常工作

- 在嵌入式系统设计中,用来进行系统初始代码调试的接口称为(D)。

A. PCI接口

B. USB接口

C. 网络接口

D. JTAG接口

6 SPI接口基本原理与结构

- SPI接口简介

- SPI接口基本原理

- SPI接口工作模式

6.1 SPI接口简介

SPI(Serial Peripheral Interface,串行外围设备接口)是由Motorola公司开发的一个低成本、易使用的接口,主要用在微处理器(MCU)和外围设备芯片之间进行连接。

- SPI接口可以用来连接存储器、AD转换器、DA转换器、实时时钟日历、LCD驱动器、传感器、音频芯片,其他处理器等。

SPI是一个4线接口,主要使用4个信号。

- 主机输出/从机输入(MOSI)

- 主机输入/从机输出(MISO)

- 串行SCLK或SCK

- 外设片选( $\overline{\text{CS}}$ )

- 有些处理器有SPI接口专用的芯片选择,称为从机选择( $\overline{\text{SS}}$ )

MOSI信号由主机产生,从机接收。

- 在有些芯片上,MOSI只被简单的标为串行输入(SI),或者串行数据输入(SDI)。

MISO信号由主机产生,不过还是在主机的控制下产生的。

- 在一些芯片上,MISO有时被称为串行输出(SO)或串行数据输出(SDO)。

外设片选信号:通常只是由主机的备用I/O引脚产生的。

与标准的串行接口不同,SPI是一个同步协议接口,所有的传输都参照一个共同的时钟,这个同步时钟信号由主机(处理器)产生,接收数据的外设(从设备)使用时钟来对串行比特流的接收进行同步化。

- 可以将多个具有SPI接口的芯片连到主机的同一个SPI接口上,主机通过控制从设备的片选输入引脚来选择接收数据的从设备。

6.2 SPI接口基本原理

如图所示,微处理器通过SPI接口与外设进行连接。

- 主机和外设都包含一个串行移位寄存器,主机写入一个字节到它的SPI串行寄存器,SPI寄存器通过MOSI信号线将字节传送给外设。

- 外设也可以将自己移位寄存器中的内容通过MISO信号线传送到主机。主机和外设的两个移位寄存器中的内容被互相交换。

- 外设的写操作和读操作是同步完成的,因此SPI成为一个很有效的协议。

如果只是进行写操作,主机只需忽略收到的字节。

如果主机要读取外设的一个字节,就必须发送一个空字节来触发从机的数据传输。

当主机发送一个连续的数据流时,有些外设能进行多字节传输。

- 如多数具有SPI接口的存储器芯片都以这种方式工作。在这种传输方式下,SPI外设的芯片选择端必须在整个传输过程中保持低电平。

- 如,存储器芯片会希望在一个“写”命令之后紧接着收到的是4个地址字节(起始地址),这样后面接收到的数据就可以存储到该地址。

其他外设只需要一个单字节(比如一个发给AD转换器的命令),有些甚至还支持菊花链连接,如图所示。

- 主机处理器从其SPI接口发送3个字节的数据

- 第1个字节发送给外设A,当第2个字节发送给外设A的时候,第1个字节已移出了A,而传送给了B

- 同样,主机想要从外设A读取一个结果,它必须要再发送一个3字节(空字节)的序列,这样就可以把A中的数据移到B中,然后再移到C中,最后送回到主机。在这个过程中,主机还依次从B和C接收到字节。

注意,菊花链连接不一定适用于所有的SPI设备,特别是要求多字节传输的(比如存储器芯片)设备。有的外设西片不支持菊花链连接。

6.3 SPI接口工作模式

根据时钟极性和时钟相位的不同,SPI有4种工作模式。

- 时钟极性有高电平、低电平两种

- 时钟相位有两个:时钟相位0和时钟相位1

时钟极性(CPOL:Clock Polarity)。

- 时钟极性为低电平时:空闲时时钟(SCK)处于低电平,传输时跳转到高电平

- 时钟极性为高电平时:空闲时时钟(SCK)处于高电平,传输时跳转到低电平

时钟相位(CPHA:Clock Phase)。

- 当CPHA为0时,时钟周期的前一边缘采集数据

- 当CPHA为1时,时钟周期的后一边缘采集数据

四种工作模式下的SCLK表现如下。

- 红线表示采集数据,下面的一个例子是S3C2440上面SPI控制器的总线范例。

6.4 例题

- 以下四种串行总线中,一组总线上不能挂连多个器件的是(A)。

A. RS232

B. RS485

C. $I^2C$

D. SPI

7 IIC接口基本原理与结构

- IIC接口简介

- IIC总线的数据传送

- IIC总线工作原理

IIC Bus(Inter Integrated Circuit BUS,内部集成电路总线)是由Philips公司推出的二线制串行扩展总线,用于连接微控制器及其外围设备。

- IIC总线是具备总线仲裁和高低速设备同步等功能的高性能多主机总线

- 直接用导线连接设备,通信时无需片选信号

- IIC总线的协议层包括物理层和数据链路层。物理层有两根信号线,在链路层每个连接到IIC总线上的设备都有唯一的地址

7.1 IIC接口简介

在IIC总线上,物理层只需要两条线一串行数数据SDA线、串行时钟SCL线,它们用于总线上器件之间的信息传递。

- SDA和SCL都是双向的

- 每个器件都有一个唯一的地址以供识别,而且各器件都可以作为一个发送器或接收器(由器件的功能决定的)。

7.2 操作模式

IIC总线有4中操作模式。

- 主发送模式

- 主接收模式

- 从发送模式

- 从接收模式

7.3 启动信号

IIC总线的启动信号。

- 当IIC接口处于从模式时,要想数据传输,必须检测SDA线上的启动信号,启动信号由主器件产生

- 在SCL信号为高时,SDA产生一个由高变低的电平变化,即产生一个启动信号

- 当IIC总线上产生了启动信号后,那么这条总线就被发出启动信号的主器件占用了,变成”忙“状态

7.4 读写数据

主器件产生一个启动信号后,会立即送出一个从地址,用来通知将与它进行数据通信的从器件。

- 1个字节的地址包括7位的地址信息和1位的传输方向指示位(R/W)

- 如果第7位为“0”,表示主机发送数据(W),即进行一个写操作

- 如果“1”,表示主机接收数据(R),即进行一个读操作

7.5 数据传输格式

数据传输格式。

- SDA线上传输的每个字节长度都是8位,每次传输中字节的数量是没有限制的。

- 在起始条件后面的第一个字节是地址域,之后每个传输的字节后面都有一个应答(ACK)位(即一帧共有9位)

- 传输中串行数据的MSB(字节的高位)首先发送

7.6 应答信号

应答信号。

- 为了完成1个字节的传输操作,接收器应该在接收完1个字节之后发送ACK位到发送器,告诉发送器,已经收到了这个字节。

- ACK脉冲信号在SCL线上第9个时钟处发出(前面8个时钟完成1个字节的数据传输,SCL上的时钟都是由主器件产生的)。

- 当发送器要接收ACK脉冲时,应该释放SDA信号线,即将SDA置高。

- 接收器在接收完前面的8位数据后,将SDA拉低。

- 发送器探测到SDA为低,就认为接收器成功接收了前面的8位数据。

7.7 IIC总线工作原理

总线竞争的仲裁。

- IIC总线上可以挂接有多个器件,有时会发生两个或多个主器件同时想占用总线的情况

- IIC总线具有多主控制能力可对发生在SDA线上的总线竞争进行仲裁

- 仲裁原则:当多个主器件同时想占用总线时,如果某个器件发送高电平,而另一个主器件发送低电平,则发送电平与此时SDA总线电平不符的那个器件将自动关闭其输出级

总线竞争的仲裁在两个层次上进行的。

- 首先是地址位的比较,如果主器件寻址同一个从器件,则进入数据位的比较,从而确保了竞争仲裁的可靠性

- 由于是利用IIC总线上的信息进行仲裁,不会造成信息的丢失

IIC总线的数据传输过程。

- 开始:主设备产生启动信号,表明数据传输开始。

- 地址:主设备发送地址信息,包含7位的从设备地址和1位的数据方位指示位(读或写位,表示数据流的方向)。

- 数据:数据指示位,数据在主设备和从设备之间进行传输。数据一般以8位传输,MSB先传;具体能传输多少量的数据并没有限制。接收器产生1位的ACK(应答信号)表明收到了每个字节。传输过程可以被中止和重新开始。

- 停止:注射别产生停止信号,结束数据传输。

7.8 例题

- 关于IIC总线,下列说法错误的是(B)。

A. IIC总线有4种操作模式:主发送模式、主接收模式、从发送模式和从接收模式

B. 传输中串行数据的LSB首先发送

C. IIC总线的数据传输过程包括了开始、地址、数据和停止信号的产生

D. IIC总线上,只需要两条线——串行数据SDA线、串行时钟SCL线,它们用于总线上器件之间的信息传递,并且都是双向的

- IIC总线协议包含物理层和数据链路层,下图是常见的多个IIC设备接口示意图,下面描述不正确的是()。

A. 在物理层,IIC使用两条信号线,一条是串行数据线,一条是串行时钟线

B. 在数据链路层,每个IIC设备不用具有唯一的设备地址

C. 在IIC构成系统中,可以多主系统,但任一时刻只能有一个主IIC设备

D. IIC具有总线仲裁功能

8 网络接口

- 以太网接口基本原理与结构

- CAN总线接口基本原理与结构

- 无线以太网基本原理与结构

- 1394接口基本原理与结构

8.1 以太网接口基本原理与结构

- 以太网基础知识

- 嵌入式以太网接口的实现方法

- 网络编程接口

8.2 以太网基础知识

以太网(Ethernet)是目前应用最广泛的局域网通讯方式,同时也是一种协议。

以太网协议定义了一系列软件和硬件标准,从而将不同的设备连接在一起。

嵌入式系统通常使用的以太网协议是IEEE802.3协议。

- 以太网接口电路主要由媒质接入控制MAC控制器和物理层接口(Physical Layer,PHY)两大部分构成

8.3 传输编码

在802.3版本的标准中,没有采用直接的二进制编码(即用0v表示“0”,用5v表示“1”),而是采用。

- 曼彻斯特编码(Manchester Encoding)

- 差分曼彻斯特编码(Differential Manchester Encoding)

曼彻斯特编码的规律。

- 每位中间有一个电平跳变,从高到低的跳变表示“0”,从低到高的跳变表示”1“。

差分曼彻斯特编码的规律。

- 每位的中间有一个电平跳变,但不用这个跳变来表示数据,而是利用每个码元开始有无跳变来表示“0”或“1”,有跳变表示“0”,无跳变表示“1”(保持性)。

曼彻斯特编码和差分曼彻斯特编码相比,前者编码简单,后者能提供更好的噪声抑制性能。

- 在802.3系统中,采用曼彻斯特编码,其高电平为+0.85v,低电平信号为-0.85v,这样指令信号电压仍然是0v。

8.4 802.3Mac层的帧

802.3 Mac层的以太网的物理传输帧如表所示。

| PR | SD | DA | SA | TYPE | DATA | PAD | FCS |

|---|---|---|---|---|---|---|---|

| 56位 | 8位 | 48位 | 48位 | 16位 | 不超过1500字节 | 可选 | 32位 |

- PR:同步位,用于收发双方的时钟同步,同时也指明了传输的速率,是56位的二进制数101010101010…,最后2位是10。

- SD:分隔位,表示下面跟着的是真正的数据而不是同步时钟,为8位的10101011。

- DA:目的地址,以太网的地址为48位二进制地址,表明该帧传输给哪个网卡。如果为FFFFFFFFFFFF,是广播地址。广播地址的数据可以被任何网卡接收到。

- SA:源地址,48位,表明该帧的数据是哪个网卡发的,即发送端的网卡地址,是6个字节。

- TYPE:类型字段,表明该帧的数据是什么类型的数据,不同协议的类型字段不同。如:0800H表示数据为IP包,0806H表示数据为ARP包,814CH是SNMP包,8137H为IPX/SPX包。

- DATA:数据段,该段数据不能超过1500B,以太网规定整个传输包的最大长度不能超过1514B(14B为DA,SA,TYPE)。

- PAD:填充位。以太网帧传输的数据包最小不能小于60B,(除去DA、SA、TYPE的14B),还必须传输46B的数据,当数据段的数据不足46B时,后面通常是补0(也可以补其他值)。

- FCS:32位数据校验位。32位的CRC校验,该校验由网卡自动计算,自动生成,自动校验,自动在数据段后面填入。不需要软件管理。

PR、SD、PAD、FCS数据段是网卡(包括物理层和Mac层的处理)层自动产生的,剩下的DA、SA、TYPE、DATA4个段的内容由上层软件控制。

8.5 以太网数据传输的特点

以太网数据传输的特点。

- 所有数据位的传输由低位开始,传输的位流用曼彻斯特编码。

- 以太网是基于冲突检测的总线复用方法,冲突退避算法是由硬件自动执行。

- 以太网传输的数据段的长度,DA + SA + TYPE + DATA + PAD最小为60B,最大为1514B。

- 通常的以太网卡可以接收3种地址的数据:广播地址、多播地址(或者叫组播地址,在嵌入式系统中很少用到)、自己的地址。但有时,用于网络分析和监控,网卡也可以设置为接收任何数据包。

- 任何两个网卡的物理地址都是不一样的,是世界上唯一的,网卡地址由专门机构分配。不同厂家使用不同地址段,同一厂家的任何两个网卡的地址也是唯一的。根据网卡的地址段(网卡地址的前3个字节)可以知道网卡的生产厂家。

8.6 以太网接口实现的方法

嵌入式处理器 + 网卡芯片。

- 把以太网芯片连接到嵌入式处理器的总线上。

- 通用性强,对嵌入式处理器没有特殊要求,不受处理器的限制,但是,嵌入式处理器和网络数据交换通过外部总线(通常是并行总线)交换数据,速度慢,可靠性不高,电路板走线复杂。

- 目前常见的以太网接口芯片,如CS8900、RTL8019/8029/8039、DM9008及DWL650无线网卡等。

带有以太网接口的嵌入式处理器。

- 常有以太网接口的嵌入式处理器通常是面向网络应用而设计的,要求嵌入式处理器有通用的网络接口(比如:MII接口)。

- 处理器和网络数据交换通过内部总线,速度快。

8.7 网络编程接口

BSD套接字(BSD Sockets)是使用的最广泛的网络程序编程方法。

- 主要用于应用程序的编写,用于网络上主机与主机之间的相互通信。

- 很多操作系统都支持BSD套接字编程。例如,UNIX、Linux、VxWorks、Windows的Winsock基本上是来自BSD Sockets。

套接字(Sockets)分为Stream Sockets和Data Sockets。

- Stream Sockets是可靠性的双向数据传输,对应使用TCP协议传输数据

- Data Sockets是不可靠连接,对应使用UDP协议传输数据

8.8 例题

略

9 CAN总线接口基本原理与结构

- CAN总线概述

- 在嵌入式处理器上扩展CAN总线接口

9.1 CAN总线概述

CAN(Controller Area Netword,控制器局域网)是德国Bosch公司于1983年为汽车应用而开发的,它是一种现场总线(FieldBus),能有效支持分布式控制和实时控制的串行通信网络。

- 1993年11月,ISO正式颁布了控制器局域网CAN国际标准(ISO11898)。

CAN总线是一种多主方式的串行通信总线。

- 理想的由CAN总线构成的单一网络中,是可以挂接任意多个节点,实际应用中节点数目受网络硬件的电气特性所限制。例如:当使用Philips P82C250作为CAN收发器时,同一网络中允许挂接110个节点。

- CAN总线具有很高的实时性能,已经在汽车工业、航空工业、工业控制、安全防护等领域中得到了广泛应用。

CAN总线的通信介质可采用双绞线、同轴电缆和光导纤维,最常用的是双绞线。

- 通信距离与波特率有关,最大通信距离可达10km,最大通信波特率可达1Mbps。

- CAN总线仲裁采用11位标识和非破坏性位仲裁总线结构机制,可以确定数据块的优先级,保证在网络节点冲突时最高优先级节点不需要冲突等待。

- CAN总线采用了多主竞争式总线结构,具有多主站运行和分散仲裁的串行总线以及广播通信的特点。

- CAN总线上任一节点可在任一时刻主动向网络上其他节点发送信息而不分主次,因此可在各节点之间实现自由通信。

CAN总线信号使用差分电压传送。

- 两条信号线被称为CAN_H和CAN_L,静态时均是2.5v左右,此时状态表示为逻辑1,也可以叫作“隐形”。

- 采用CAN_H比CAN_L高表示逻辑0,称为“显性”,通常电压值为CAN_H = 3.5v和CAN_L = 1.5v。

- 当“显性”位和“隐性”位同时发送的时候,最后总线数值降为“显性”。

- 这种特性为CAN总线的仲裁奠定了基础。

9.2 CAN总线接口

一些面向工业控制的嵌入式处理器集成了一个或者多个CAN总线控制器。

- 例如:Phillips公司的LPC2194和LPC2294(ARM7TDMI内核)带有4个CAN总线控制器。

- CAN总线控制器主要是完成时序控制逻辑转换等工作,要在电气特性上满足CAN总线标准,还需要一个CAN总线的物理层芯片,用它来实现TTL电平到CAN总线电平特性的转换,即CAN收发器。

实际上,多数嵌入式处理器都不带CAN总线控制器。

- 通常的解决方案是在嵌入式处理器的外部总线上扩展CAN总线接口芯片。

- 例如:Phillips公司的SJA1000 CAN总线接口芯片,Microchip公司的MCP251x系列(MCP2510和MCP2515)CAN总线接口芯片,这两种芯片都支持CAN2.0B标准。

- SJA 1000的总线采用的是地址线和数据线复用的方式,多数嵌入式处理器采用SJA 1000扩展CAN总线较为复杂。

9.3 嵌入式处理器上扩展CAN总线接口

MCP2510是由Microchip公司生产的CAN协议控制器,完全支持CAN总线V2.0A/B技术规范。

- 0~8字节的有效数据长度,支持远程帧

- 最大1Mb/s的可编程波特率

- 两个支持过滤波器(Filter,Mask)的接收缓冲区,三个发送缓冲区

- 支持回环(Loop Back)模式,便于测试

- SPI高速串行总线,最大5MHz

- 3v到5.5v供电

大多数嵌入式处理器都有SPI总线控制器,MCP2510可以3v到5.5v供电,能够直接和3.3v I/O口的嵌入式处理器连接,电路原理图如图所示。

MCP2510使用3.3v电压供电,可以直接和三星S3C44B0X处理器通过SPI总线连接。相关的资源如下。

- 使用一个扩展的I/O口(EXIO2)作为片选信号,电平有效。

- 用S3C2410A的外部中断6(EXINT6)作为中断管脚,低电平有效。

- 16MHz晶体作为输入时钟,MCP2510内部有晶振电路,用晶体可以直接起振使用TJA1050作为CAN总线收发器。

CAN总线收发器TJA1050必须使用5v供电。MCP2510和TJA1050连接的两个信号都是单向的信号。需要满足I/O口的电气特性。

- 从MCP2510输出的TXCAN信号是否满足TJA1050的输入电平。TJA1050位5v供电时,输入高电平 $V_{ih}$ 的范围是2~5.3v。而3.3v供电的MCP2510输出TXCAN信号高电平 $V_{oh}$ 最小值为2.6v,可以满足要求。

- 从TJA1050输出的RXD信号是否满足MCP2510的输入电平。3.3v供电的MCP2510输入信号RXCAN高电平范围 $V_{ih}$ :2~4.3v,无法满足5v逻辑的TJA1050输出电平,电阻分压实现单向电平转换。

分压电阻值的选择,需要考虑2个问题。

- TJA1050输出信号的驱动能力(输出电流 $\leq 15mA$ )

- MCP2510的RXCAN管脚的输入阻抗(输入电流 $\leq 5μA$ )

10 无线以太网基本原理与结构

- WLAN简介

- WLAN标准

10.1 WLAN简介

WLAN(Wireless Local Area Network,无线局域网)是利用无线通信技术在一定局部范围内建立的,是计算机网络与无线通信技术相结合的产物,以无线多址通道作为传输媒介,提供有线局域网的功能。

传输介质。

- 红外线IR

- 射频RF波段

10.2 WLAN标准

WLAN的标准:主要是针对物理层和媒质访问控制层(MAC层)。

- 涉及到所有使用的无线频率范围、控制接口通信协议等技术规范与技术标准。

11 IEEE 1394接口基本原理与结构

- IEEE 1394简介

- IEEE 1394的特点

- IEEE 1394的协议结构

11.1 IEEE 1394简介

IEEE 1394是Apple公司率先提出的一种高品质、高传输速率的串行总线技术,1995年被IEEE认定为串行工业总线标准。

- 1394作为一种标准总线,可以在不同的工业设备之间架起一座沟通的桥梁

- 在一条总线上可以接入63个设备

- 实时多媒体领域,大容量存储以及打印机、扫描仪上等等

- IEEE 1394规范仅支持64位固定解址模式

11.2 IEEE 1394的特点

支持多种总线速度,适应不同应用要求。

- IEEE 1394a:100Mb/s、200Mb/s、400Mb/s

- IEEE 1394b:800Mb/s、1600Mb/s、3200Mb/s

支持热插拔。

- 设备的资源均由总线控制器自动分配

- 总线控制器会自动重新配置好设备

接口有两种类型。

- 6针的六角形接口和4针的小型四角形接口

- 6针的六角形接口可向所连接的设备供电,而4针的四角形接口则不能

支持同步和异步两种传输方式。

- 设备可以根据需要动态地选择传输方式,总线自动完成带宽分配

- 要求实时传输并对数据的完整性要去不严格的场合,可采用同步传输方式

- 对数据完整性要求较高的场合,采用异步传输方式更好

支持点到点通信模式,IEEE 1394是多主总线。

- 每个设备均可以获取总线的控制权,与其他设备进行通信。

两种传输方式:Backplane模式和Cable模式。

- Backplane模式最小的速率也比USB1.1最高速率高,分别为12.5Mbps/s、25Mbps/s、50Mbps/s,可以用于多数的高带宽应用。

- Cable模式是速度非常快的模式,分为100Mbps/s、200Mbps/s和400Mbps/s几种,在200Mbps/s下可以传输不经压缩的高质量数据电影。

遵循ANSI IEEE 1212控制及状态寄存器(CSR)标准,定义了64位的地址空间。

- 可寻址1024条总线的63个节点,每个节点包含256TB的内存空间

支持较远距离的传输。

- 普通线缆:2个设备之间的最大距离可达4.5m(高级线缆可达15m)

- 玻璃光缆或5类双绞线:设备间距离可达100m以上。

支持公平仲裁原则,为每一种传输方式保证足够的传输带宽。

- 支持错误检测和处理。

六线电缆具有电源线,可传输8~40v的直流电压。

- 2对双绞线:信号传递

- 1对双绞线:供应电源

11.3 IEEE 1394的协议结构

IEEE 1394的协议栈由3层组成:物理层、链路层和事务层,另外还有一个管理层。

- 物理层和链路层由硬件构成,通常集成在同一块芯片上

- 事务层主要由软件实现

物理层提供IEEE1394的电气和机械接口,功能是重组字节流并将它们发送到目的节点上去。

- 物理层为链路层提供服务

- 解析字节流并发送数据包给链路层

链路层提供了给事务层确认的数据服务,包括:寻址、数据组帧和数据校验。

- 提供直接面向应用的服务

- 支持同步和异步传输模式

- 链路层的底层提供了仲裁机制

11.4 例题

- IEEE 1394具有(D)位地址空间,IEEE 1394的通信协议具有三个协议包,不包括(B)。

(1)

A. 8

B. 16

C. 32

D. 64

(2)

A. 事物层

B. 表示层

C. 链路层

D. 物理层

12 总线分类

| 总线分类 | 说明 | 常用总线 |

|---|---|---|

| 内部总线 | 内部总线是微处理机内部各外围芯片与处理器之间的总线,用于芯片一级的互连 | IIC总线、SPI总线、SCI总线等 |

| 系统总线 | 系统总线是微机中各插件板与系统板之间的总线,用于插件板一级的互连 | ISA总线、EISA总线、VESA总线、PCI总线等 |

| 外部总线 | 外部总线则是微机和外部设备之间的总线,微机作为一种设备,通过该总线和其他设备进行信息与数据交换,它用于设备一级的互连 | RS232、RS485、USB总线、IEEE1394总线等 |

12.1 例题

- 以下关于嵌入式系统总线的描述中,不正确的是(C)。

A. 异步通信时数据是一帧一帧传送的,没帧数据的传送靠起始位来同步

B. SPI、IIC、UART都属于串行通信方式

C. 同步通信方式是字符同步,且在字符与字符之间的时序仍然是同步的

D. RS232、RS485、USB、IEEE1394总线都属于外部总线

- 不属于系统总线的是(C)。

A. ISA

B. EISA

C. SCSI

D. PCI

2.2.2 半双工

半双工通信:数据可以从设备A到设备B进行传输,也可以从设备B到设备A进行传输,但不能在同一时刻进行双向传输。如:对讲机。

第十四章——嵌入式系统总线和通讯接口

前言:

计算机第十四章节主要知识点。

1 知识点介绍

- 串行接口基本原理与结构

- 并行接口基本原理与结构

- PCI接口基本原理与结构

- USB接口基本原理与结构

- SPI接口基本原理与结构

- IIC接口基本原理与结构

- 网络接口基本原理与结构

- 总线分类

2 串行接口基本原理与结构

- 串行通信概述

- RS-232C串行接口

- RS-422串行通信接口

- RS-485串行总线接口

2.1 串行通信概述

串行通信:数据是一位一位地进行传输的,在传输中每一位数据都占据一个固定的时间长度。

优点。

- 传输线少、成本低

- 特别适合远距离传送

缺点。

- 速度慢

2.2 串行通信模式

2.2.1 单工

串行数据传送有3种基本的通信模式:单工、半双工、全双工通信。

单工通信:数据仅能从设备A到设备B进行单一方向的传输。如遥控、遥测等。

2.2.2 半双工

半双工通信:数据可以从设备A到设备B进行传输,也可以从设备B到设备A进行传输,但不能在同一时刻进行双向传输。如:对讲机。

2.2.3 全双工

全双工通信:数据可以在同一时刻从设备A传输到设备B,或从设备B传输到设备A,即可以同时双向传输。如电话。

2.2.4 串行通信异步

串行通信在信息格式上可以分为:异步通信和同步通信方式。

异步通信方式。

- 是指通信的发送与接收设备使用各自的时钟,控制数据的发送和接收过程。

- 为使双方的收发协调,要求发送和接收设备的时钟尽可能一致。

异步通信方式。

- 数据是一帧一帧传送的,没帧数据包含有起始位(“0”)、数据位、奇偶校验位和停止位(“1”),每帧数据的传送靠起始位来同步。

- 一帧数据的各位代码间的时间间隔是固定的,而相邻两帧的数据其时间间隔是不固定的。

- 在异步通信的数据传送中,传输线上允许空字符。

字符格式。

- 异步通信对字符格式、波特率、校验位有确定的要求。

字符格式。

- 每个字符传送时,必须前面加一位起始位,后面加上1、1.5或2位停止位。

- 例如ASCII码传送时,一帧数据的组成是:前面1个起始位,接着7位ASCII编码,再接着一位奇偶校验位,最后一位停止位,共10位。

2.2.5 波特率和校验位

波特率。

- 传送数据位的速率称为波特率,用位/秒(bit/s)来表示,称之为波特。

- 例如,数据传送的速率为120字符/秒,每帧包括10个数据位,则传送波特率为: $10 \times 120 = 1200b/s = 1200波特$

- 异步通信的波特率的数值通常为:150、300、600、1200、2400、4800、9600、14400、28800等,数值成倍数变化。

校验位。

- 偶校验就是要使字符加上校验位有偶数个“1”。

- 奇校验就是要使字符加上校验位有奇数个“1”。

- 例如数据“00010011”,共有奇数个“1”,偶校验时,则校验位就置为“1”,奇校验时,则校验位就置为“0”。

2.2.6 串行异步特点

异步通信的特点。

- 不要求收发双方时钟的严格一致,实现容易,设备开销较小。

- 但每个字符要附加2~3位用于起始,各帧之间还有间隔,因此传输效率不高。实际使用率只有约80%。

2.2.7 串行通信同步

同步通信。

- 是一种比特同步通信技术,要求收发双方具有同频同相的同步时钟信号,只需在传送报文的最前面附加特定的同步字符,使收发双方建立同步,此后便在同步时钟的控制下逐位发送/接收。

- 同步传输采用字符块的方式,减少每一个字符的控制和错误检测数据位,因而可以具有较高的传输速率。

- 即将许多字符聚集成一字符块后,在每块信息之前要加上1~2个同步字符,字符块之后再加入适当的错误检测数据才传送出去。

特点。

- 数据传输速率较高。

- 但要求发送方时钟和接收方时钟保持严格同步。

2.2.8 串口同步和异步发送

2.3 RS-232C串行接口

2.3.1 接口规格

RS-232C是美国电子工业协会(EIA)制定的一种串行通信接口标准。

RS-232C接口规格。

- EIA所制定的传送电气规格如下表所示。

- RS-232C通常以±12v的电压来驱动信号线,TTL标准与RS-232C标准之间的电平转换电路通常采用集成电路芯片实现,如M2AX23等。

| 状态 | L(Low) | H(Hight) |

|---|---|---|

| 电压范围 | -25~-3v | +3v~25v |

| 负逻辑 | 1 | 0 |

2.3.2 接口信号

EIA制定的RS-232C接口与外界的相连采用25芯(DB-25)和9芯(DB-9)D型插接件,实际应用中,并不是每只引脚信号都必须用到。

2.3.3 引脚功能

RS-232C DB-9各引脚功能如下。

| 引脚号 | 符号表示 | 名称 | 说明 |

|---|---|---|---|

| 1 | CD | 载波检测 | 主要用于Modem通知计算机其处于在线状态,即Modem检测到拨号音 |

| 2 | RXD | 接收数据线 | 用于接收外部设备送来的数据 |

| 3 | TXD | 发送数据线 | 用于将计算机的数据发送给外部设备 |

| 4 | DTR | 数据终端 | 当次引脚高电平时,通知Modem可以进行数据传输,计算机已经准备好 |

| 5 | SG | 信号地 | |

| 6 | DSR | 数据设备就绪 | 此引脚为高电平时,通知计算机Modem已经准备好,可以进行数据通信 |

| 7 | RTS | 请求发送 | 此引脚由计算机来控制,用以通知Modem马上传送数据至计算机,否则Modem将收到的数据暂时放入缓冲区中 |

| 8 | CTS | 允许发送 | 此引脚由Modem控制,用以通知计算机将要传送的数据送至Modem |

| 9 | RI | 振铃提示 | Modem通知计算机有呼叫进来,是否接听呼叫由计算机决定 |

2.3.4 连接方式

RS-232C的基本连接方式。

- 计算机利用RS-232C接口进行串口通信,有简单连接和完全连接两种连接方式

- 简单连接又称三线连接,即只连接发送数据线、接收数据线和信号地,实现全双工通信

- 如果应用中还需要使用RS-232C的控制信号,则采用完全连接方式。

2.4 RS-422串行接口

RS-422标准是RS-232的改进型,是一种可单机发送多机接收的平衡传输规范,传输速率可达10Mb/s。采用差分传输方式,也称平衡传输。

- 允许在相同传输线上连接多个接收节点,最多可接10个节点,即一个主设备(Master),其余10个为从设备(Slave),从设备之间不能通信。

- 支持一点对多点的双向通信。RS-422四线接口由于采用单独的发送和接收通道,因此不必控制数据方向,各装置之间任何必须的信号交换均可以按软件方式(XON/XOFF握手)或硬件方式(一对单独的双绞线)实现。

RS-422的最大传输距离为4000英尺(约1219m),最大传输速率为10Mb/s。

- 传输速率与平衡双绞线的长度有关,只有在很短的距离下才能获得最高传输速率

- 在最大传输距离时,传输速率为100kb/s

- 一般100m长的双绞线上所能获得的最大传输速率仅为1Mb/s

RS-422需要在传输电缆的最远端连接一个电阻,要求电阻阻值约等于传输电缆的特性阻抗。

- 在短距离(300m以下)传输时可以不连接电阻。

2.5 RS-485串行接口

在RS-422的基础上,为扩展应用范围,EIA制定了RS-485标准,增加了多点、双向通信能力。

- 在通信距离为几十米至上千米时,通常采用RS-485接收器

- RS-485接收器采用平衡发送和差分接收

- 即在发送端,驱动器将TTL电平信号转换成差分信号输出,在接收端,接收器将差分信号变成TTL电平,因此具有抑制共模干扰的能力。

- 接收器能够检测低达200mv的电压,具有高的灵敏度,故数据传输距离可达千米以上。

RS-485可以采用二线与四线方式,二线制可以实现真正的多点双向通信。

- 采用四线连接时,与RS-422一样只能实现点对点的通信,即只能有一个主设备,其余为从设备。

- RS-485可以连接多达32个设备

RS-485的共模输出电压在-7~+12v之间,接收器最小输入阻抗为12kΩ。

RS-485满足所有RS-422的规范,所以RS-485的驱动器可以在RS-422网络中应用。

RS-485的最大传输速率为10Mb/s。在最大传输距离时,传输速率为100kb/s。

RS-485需要两个终端电阻,接在传输总线的两端,要求电阻阻值约等于传输电缆的特性阻抗。

- 在短距离传输(在300m以下)时可不需终端电阻。

2.6 例题

- 使用串行总线传输数据时,被传输的数据(D)。

A. 在发送设备和接收设备中都是进行串行到并行的变换

B. 在发送设备和接收设备中都是进行并行到串行的变换

C. 在发送设备中进行串行到并行的变换,接收设备中进行并行到串行的变换

D. 在发送设备中进行并行到串行的变换,接收设备中进行串行到并行的变换

3 并行接口基本原理与结构

- 并行接口分类

- 并行总线

3.1 并行接口基本概念

并行通信通常是将数据字节的各位用多条数据线同时进行传送。

- 一般用来连接打印机、扫描仪等,所以又称打印口。

特定。

- 控制简单,传输速度快

- 由于传输线较多,长距离传送时成本高且接收方的各位同时接收存在的困难。

3.2 并行接口分类

并行接口可以分为。

- SPP(标准并口)

- EPP(增强型并口)

- ECP(扩展型并口)

3.3 并行总线分类

&emsep; 并行总线分为。

- 标准并行总线

- 非标准并行总线

常用的并行标准总线:IEEE488总线和SCSI总线。

总线是一种高性能非标准的通用多用户并行总线。

3.4 并行总线IEE488

IEEE488总线。

- 又称GPIB总线(General Purpose Interface Bus,通用接口总线)

- 位并行、字节串行双向异步方式传输信号

- 总线方式连接,仪器设备直接并联于总线上,总线上最多可连接15台设备

- 最大传输距离为20m,信号传输速度一般为500kb/s,最大传输速度为1Mb/s

- 广泛应用在仪器、仪表、测控领域

3.5 并行总线SCSI和MXI

SCSI(Small Computer System Interface,小型计算机系统接口)总线。

- 速度可达5Mb/s,传输距离6m

- 传输速率很高

- 普通用作计算机的高速外设总线,如连接高速硬盘驱动器

MXI总线(Multi-system Extension Interface bus,多系统扩展接口总线)。

- 是一种高性能非标准的通用多用户并行总线

- 32位高速并行总线

- 最高速度可达23Mb/s,传输距离20m

- 用作计算机与测控机箱的互连

3.6 例题

- 串行总线与并行总线比,(C)。

A. 串行总线成本高,速度快

B. 串行总线成本高,速度慢

C. 并行总线成本高,速度快

D. 并行总线成本低,速度快

- 信息可以在两个方向上同时传输的总线属于(C)。

A. 单工总线

B. 半双工总线

C. 全双工总线

D. 单向总线

- 以下关于总线的叙述中,不正确的是(C)。

A. 并行总线适合近距离高速数据传输

B. 串行总线适合长距离数据传输

C. 单总线结构在一个总线上适合不同种类的设备,设计简单且性能很高

D. 专用总线在设计上可以与连接设备实现最佳匹配

4 PCI接口基本原理与结构

- PCI接口基本结构

4.1 PCI接口基本结构

PCI(Peripheral Component Interconnect,外围设备互连)总线是由Intel公司推出的一种局部总线,是当前用于系统扩展最流行的总线之一。

PCI总线是地址、数据多路复用的高性能32位和64位总线,是微处理器与外围控制部件、外围附加板之间的互连机构。

PCI定义了32位数据总线,并且可扩展为64位。总线速度有32MHz和66MHz两种。

- 改良的PCI系统PCI-X,数据传输速度最高可以达到64位@133MHz

- PCI总线主板插槽的体积比ISA总线插槽小,支持突发读写操作(突发数据传输),可同时支持多组外围设备

与ISA总线不同,PCI总线的地址总线与数据总线是分时复用的,支持即插即用(PNP:Plug-and-Play)、中断共享等功能。

PCI总线在数据传输时,由一个PCI设备做发起者(称为Master、Initator),而另一个PCI设备做目标(称为Slave、Target)。

- 总线上所有时序的产生与控制都由Master发起

- PCI总线在同一时刻只能供一对设备完成传输,要求有一个仲裁机构来决定谁有权拿到总线的主控权

4.1.1 例题

- 关于PCI总线,下列说法不正确的是(A)。

A. PCI总线是地址、数据多路复用的一种总线,不支持即插即用,支持中断共享功能

B. PCI定义了32位数据总线,也可扩展为64位总线

C. PCI总线在数据传输时,由一个PCI设备做发起者,而另一个PCI设备做目标

D. PCI总线要求有一个仲裁机构来决定谁有权拿到总线的主控权,所以在同一时刻只能供一对设备完成传输

- 在以下描述中PCI总线的基本概念中,正确的表述有(B)、(E)、(F)、(G)、(J)、(K)。

A. PCI总线是一个与处理器有关的高速外围总线

B. PCI总线的基本传输机制是触发传输

C. PCI设备一定是主设备

D. PCI的物理地址与其他总线一样,是由内存地址空间和I/O地址组成

E. PCI设备的地址译码不能对配置空间直接寻址

F. PCI设备识别主要是对开发商代码和设备代码进行识别

G. 访问配置空间时,PCI桥应提供IDSEL信号以选择PCI设备

H. 系统中只允许有一条PCI总线

I. PCI总线是高速串行总线

J. PCI总线有3种桥,即HOST/PCI桥,PCI/PCI桥,PCI/LEGACY桥

K. PCI桥是可以把一条总线的地址空间映射到另一条总线的地址空间

5 USB接口基本原理与结构

- USB总线的主要性能特点

- 物理接口

USB(Universal Serial Bus,通用串行总线)是由Compaq、HP、Intel、Lucent、Microsoft、NEC和Philips公司制定的连接计算机与外围设备的机外串行总线。

- 最多可连接127个设备

- 用于多种嵌入式系统设备的数据通信。如移动硬盘、PDA

5.1 热插拔

USB提供机箱外的热插拔功能,连接外设不必再打开机箱,也不必关闭主机电源,USB可智能地识别USB链上外围设备的动态插入或拆除,具有自动配置和重新配置外设的能力,连接设备方便,使用简单。

可连接多个外部设备。

- 每个USB系统中有1个主机,USB总线采用“级联”方式可连续多个外部设备。

- 每个USB设备用一个USB插头连接到上一个USB设备的USB插座上,而其本身又提供一或多个USB插座供一下一个或多个USB设备连接使用。

- 这种多重连接是通过集线器(Hub)来实现的,整个USB网络中最多可连接127个设备,支持多个设备同时操作

5.2 USB总线的主要性能特点

可同时支持不同同步传输方式和速率的设备。

- 可同时支持同步传输和异步传输两种传输方式

- 可同时支持不同速率的设备,速率最高可达几百Mb/s

- 支持主机与设备之间的多数据流和多消息流传输,且支持同步和异步传输类型

- 提供了四种不同的数据传输类型:控制传输、数据传输、中断数据传输和同步数据传输

较强的纠错能力。

- USB系统可实时地管理设备插拔

- 在USB协议中包括了传输错误管理、错误恢复等功能,同时根据不同的传输类型来处理传输错误

低成本的电缆和连接器。

- USB采用统一的4引脚插头和一根四芯的电缆传送信号和电源

- 电缆长度可达5m

总线供电。

- USB总线可以为连接在其上的设备提供5v电压/100mA电流的供电,最大可提供500mA的电流

- USB设备也可采用自供电方式,可以通过电池或其他的电力设备

- 支持节约能源的挂机和唤醒模式

5.3 USB总线的应用

5.4 USB总线物理接口

USB总线的电缆有一对标准尺寸的双绞信号线和一对标准尺寸的电源线,共4根导线。

| 连接序号 | 信号名称 | 典型连接线 |

|---|---|---|

| 1 | VBUS(USB电源) | 红 |

| 2 | D+(正差分信号) | 白 |

| 3 | D-(负差分信号) | 绿 |

| 4 | GND(USB地) | 黑 |

| 外层 | 屏蔽层 | - |

5.5 例题

- 下面关于通用串行总线USB的描述,不正确的是(D)。

A. USB接口为外设提供电源

B. USB设备可以起集线器作用

C. 可同时连接127台输入/输出设备

D. 通用串行总线不需要软件控制就能正常工作

- 在嵌入式系统设计中,用来进行系统初始代码调试的接口称为(D)。

A. PCI接口

B. USB接口

C. 网络接口

D. JTAG接口

6 SPI接口基本原理与结构

- SPI接口简介

- SPI接口基本原理

- SPI接口工作模式

6.1 SPI接口简介

SPI(Serial Peripheral Interface,串行外围设备接口)是由Motorola公司开发的一个低成本、易使用的接口,主要用在微处理器(MCU)和外围设备芯片之间进行连接。

- SPI接口可以用来连接存储器、AD转换器、DA转换器、实时时钟日历、LCD驱动器、传感器、音频芯片,其他处理器等。

SPI是一个4线接口,主要使用4个信号。

- 主机输出/从机输入(MOSI)

- 主机输入/从机输出(MISO)

- 串行SCLK或SCK

- 外设片选( $\overline{\text{CS}}$ )

- 有些处理器有SPI接口专用的芯片选择,称为从机选择( $\overline{\text{SS}}$ )

MOSI信号由主机产生,从机接收。

- 在有些芯片上,MOSI只被简单的标为串行输入(SI),或者串行数据输入(SDI)。

MISO信号由主机产生,不过还是在主机的控制下产生的。

- 在一些芯片上,MISO有时被称为串行输出(SO)或串行数据输出(SDO)。

外设片选信号:通常只是由主机的备用I/O引脚产生的。

与标准的串行接口不同,SPI是一个同步协议接口,所有的传输都参照一个共同的时钟,这个同步时钟信号由主机(处理器)产生,接收数据的外设(从设备)使用时钟来对串行比特流的接收进行同步化。

- 可以将多个具有SPI接口的芯片连到主机的同一个SPI接口上,主机通过控制从设备的片选输入引脚来选择接收数据的从设备。

6.2 SPI接口基本原理

如图所示,微处理器通过SPI接口与外设进行连接。

- 主机和外设都包含一个串行移位寄存器,主机写入一个字节到它的SPI串行寄存器,SPI寄存器通过MOSI信号线将字节传送给外设。

- 外设也可以将自己移位寄存器中的内容通过MISO信号线传送到主机。主机和外设的两个移位寄存器中的内容被互相交换。

- 外设的写操作和读操作是同步完成的,因此SPI成为一个很有效的协议。

如果只是进行写操作,主机只需忽略收到的字节。

如果主机要读取外设的一个字节,就必须发送一个空字节来触发从机的数据传输。

当主机发送一个连续的数据流时,有些外设能进行多字节传输。

- 如多数具有SPI接口的存储器芯片都以这种方式工作。在这种传输方式下,SPI外设的芯片选择端必须在整个传输过程中保持低电平。

- 如,存储器芯片会希望在一个“写”命令之后紧接着收到的是4个地址字节(起始地址),这样后面接收到的数据就可以存储到该地址。

其他外设只需要一个单字节(比如一个发给AD转换器的命令),有些甚至还支持菊花链连接,如图所示。

- 主机处理器从其SPI接口发送3个字节的数据

- 第1个字节发送给外设A,当第2个字节发送给外设A的时候,第1个字节已移出了A,而传送给了B

- 同样,主机想要从外设A读取一个结果,它必须要再发送一个3字节(空字节)的序列,这样就可以把A中的数据移到B中,然后再移到C中,最后送回到主机。在这个过程中,主机还依次从B和C接收到字节。

注意,菊花链连接不一定适用于所有的SPI设备,特别是要求多字节传输的(比如存储器芯片)设备。有的外设西片不支持菊花链连接。

6.3 SPI接口工作模式

根据时钟极性和时钟相位的不同,SPI有4种工作模式。

- 时钟极性有高电平、低电平两种

- 时钟相位有两个:时钟相位0和时钟相位1

时钟极性(CPOL:Clock Polarity)。

- 时钟极性为低电平时:空闲时时钟(SCK)处于低电平,传输时跳转到高电平

- 时钟极性为高电平时:空闲时时钟(SCK)处于高电平,传输时跳转到低电平

时钟相位(CPHA:Clock Phase)。

- 当CPHA为0时,时钟周期的前一边缘采集数据

- 当CPHA为1时,时钟周期的后一边缘采集数据

四种工作模式下的SCLK表现如下。

- 红线表示采集数据,下面的一个例子是S3C2440上面SPI控制器的总线范例。

6.4 例题

- 以下四种串行总线中,一组总线上不能挂连多个器件的是(A)。

A. RS232

B. RS485

C. $I^2C$

D. SPI

7 IIC接口基本原理与结构

- IIC接口简介

- IIC总线的数据传送

- IIC总线工作原理

IIC Bus(Inter Integrated Circuit BUS,内部集成电路总线)是由Philips公司推出的二线制串行扩展总线,用于连接微控制器及其外围设备。

- IIC总线是具备总线仲裁和高低速设备同步等功能的高性能多主机总线

- 直接用导线连接设备,通信时无需片选信号

- IIC总线的协议层包括物理层和数据链路层。物理层有两根信号线,在链路层每个连接到IIC总线上的设备都有唯一的地址

7.1 IIC接口简介

在IIC总线上,物理层只需要两条线一串行数数据SDA线、串行时钟SCL线,它们用于总线上器件之间的信息传递。

- SDA和SCL都是双向的

- 每个器件都有一个唯一的地址以供识别,而且各器件都可以作为一个发送器或接收器(由器件的功能决定的)。

7.2 操作模式

IIC总线有4中操作模式。

- 主发送模式

- 主接收模式

- 从发送模式

- 从接收模式

7.3 启动信号

IIC总线的启动信号。

- 当IIC接口处于从模式时,要想数据传输,必须检测SDA线上的启动信号,启动信号由主器件产生

- 在SCL信号为高时,SDA产生一个由高变低的电平变化,即产生一个启动信号

- 当IIC总线上产生了启动信号后,那么这条总线就被发出启动信号的主器件占用了,变成”忙“状态

7.4 读写数据

主器件产生一个启动信号后,会立即送出一个从地址,用来通知将与它进行数据通信的从器件。

- 1个字节的地址包括7位的地址信息和1位的传输方向指示位(R/W)

- 如果第7位为“0”,表示主机发送数据(W),即进行一个写操作

- 如果“1”,表示主机接收数据(R),即进行一个读操作

7.5 数据传输格式

数据传输格式。

- SDA线上传输的每个字节长度都是8位,每次传输中字节的数量是没有限制的。

- 在起始条件后面的第一个字节是地址域,之后每个传输的字节后面都有一个应答(ACK)位(即一帧共有9位)

- 传输中串行数据的MSB(字节的高位)首先发送

7.6 应答信号

应答信号。

- 为了完成1个字节的传输操作,接收器应该在接收完1个字节之后发送ACK位到发送器,告诉发送器,已经收到了这个字节。

- ACK脉冲信号在SCL线上第9个时钟处发出(前面8个时钟完成1个字节的数据传输,SCL上的时钟都是由主器件产生的)。

- 当发送器要接收ACK脉冲时,应该释放SDA信号线,即将SDA置高。

- 接收器在接收完前面的8位数据后,将SDA拉低。

- 发送器探测到SDA为低,就认为接收器成功接收了前面的8位数据。

7.7 IIC总线工作原理

总线竞争的仲裁。

- IIC总线上可以挂接有多个器件,有时会发生两个或多个主器件同时想占用总线的情况

- IIC总线具有多主控制能力可对发生在SDA线上的总线竞争进行仲裁

- 仲裁原则:当多个主器件同时想占用总线时,如果某个器件发送高电平,而另一个主器件发送低电平,则发送电平与此时SDA总线电平不符的那个器件将自动关闭其输出级

总线竞争的仲裁在两个层次上进行的。

- 首先是地址位的比较,如果主器件寻址同一个从器件,则进入数据位的比较,从而确保了竞争仲裁的可靠性

- 由于是利用IIC总线上的信息进行仲裁,不会造成信息的丢失

IIC总线的数据传输过程。

- 开始:主设备产生启动信号,表明数据传输开始。

- 地址:主设备发送地址信息,包含7位的从设备地址和1位的数据方位指示位(读或写位,表示数据流的方向)。

- 数据:数据指示位,数据在主设备和从设备之间进行传输。数据一般以8位传输,MSB先传;具体能传输多少量的数据并没有限制。接收器产生1位的ACK(应答信号)表明收到了每个字节。传输过程可以被中止和重新开始。

- 停止:注射别产生停止信号,结束数据传输。

7.8 例题

- 关于IIC总线,下列说法错误的是(B)。

A. IIC总线有4种操作模式:主发送模式、主接收模式、从发送模式和从接收模式

B. 传输中串行数据的LSB首先发送

C. IIC总线的数据传输过程包括了开始、地址、数据和停止信号的产生

D. IIC总线上,只需要两条线——串行数据SDA线、串行时钟SCL线,它们用于总线上器件之间的信息传递,并且都是双向的

- IIC总线协议包含物理层和数据链路层,下图是常见的多个IIC设备接口示意图,下面描述不正确的是()。

A. 在物理层,IIC使用两条信号线,一条是串行数据线,一条是串行时钟线

B. 在数据链路层,每个IIC设备不用具有唯一的设备地址

C. 在IIC构成系统中,可以多主系统,但任一时刻只能有一个主IIC设备

D. IIC具有总线仲裁功能

8 网络接口

- 以太网接口基本原理与结构

- CAN总线接口基本原理与结构

- 无线以太网基本原理与结构

- 1394接口基本原理与结构

8.1 以太网接口基本原理与结构

- 以太网基础知识

- 嵌入式以太网接口的实现方法

- 网络编程接口

8.2 以太网基础知识

以太网(Ethernet)是目前应用最广泛的局域网通讯方式,同时也是一种协议。

以太网协议定义了一系列软件和硬件标准,从而将不同的设备连接在一起。

嵌入式系统通常使用的以太网协议是IEEE802.3协议。

- 以太网接口电路主要由媒质接入控制MAC控制器和物理层接口(Physical Layer,PHY)两大部分构成

8.3 传输编码

在802.3版本的标准中,没有采用直接的二进制编码(即用0v表示“0”,用5v表示“1”),而是采用。

- 曼彻斯特编码(Manchester Encoding)

- 差分曼彻斯特编码(Differential Manchester Encoding)

曼彻斯特编码的规律。

- 每位中间有一个电平跳变,从高到低的跳变表示“0”,从低到高的跳变表示”1“。

差分曼彻斯特编码的规律。

- 每位的中间有一个电平跳变,但不用这个跳变来表示数据,而是利用每个码元开始有无跳变来表示“0”或“1”,有跳变表示“0”,无跳变表示“1”(保持性)。

曼彻斯特编码和差分曼彻斯特编码相比,前者编码简单,后者能提供更好的噪声抑制性能。

- 在802.3系统中,采用曼彻斯特编码,其高电平为+0.85v,低电平信号为-0.85v,这样指令信号电压仍然是0v。

8.4 802.3Mac层的帧

802.3 Mac层的以太网的物理传输帧如表所示。

| PR | SD | DA | SA | TYPE | DATA | PAD | FCS |

|---|---|---|---|---|---|---|---|

| 56位 | 8位 | 48位 | 48位 | 16位 | 不超过1500字节 | 可选 | 32位 |

- PR:同步位,用于收发双方的时钟同步,同时也指明了传输的速率,是56位的二进制数101010101010…,最后2位是10。

- SD:分隔位,表示下面跟着的是真正的数据而不是同步时钟,为8位的10101011。

- DA:目的地址,以太网的地址为48位二进制地址,表明该帧传输给哪个网卡。如果为FFFFFFFFFFFF,是广播地址。广播地址的数据可以被任何网卡接收到。

- SA:源地址,48位,表明该帧的数据是哪个网卡发的,即发送端的网卡地址,是6个字节。

- TYPE:类型字段,表明该帧的数据是什么类型的数据,不同协议的类型字段不同。如:0800H表示数据为IP包,0806H表示数据为ARP包,814CH是SNMP包,8137H为IPX/SPX包。

- DATA:数据段,该段数据不能超过1500B,以太网规定整个传输包的最大长度不能超过1514B(14B为DA,SA,TYPE)。

- PAD:填充位。以太网帧传输的数据包最小不能小于60B,(除去DA、SA、TYPE的14B),还必须传输46B的数据,当数据段的数据不足46B时,后面通常是补0(也可以补其他值)。

- FCS:32位数据校验位。32位的CRC校验,该校验由网卡自动计算,自动生成,自动校验,自动在数据段后面填入。不需要软件管理。

PR、SD、PAD、FCS数据段是网卡(包括物理层和Mac层的处理)层自动产生的,剩下的DA、SA、TYPE、DATA4个段的内容由上层软件控制。

8.5 以太网数据传输的特点

以太网数据传输的特点。

- 所有数据位的传输由低位开始,传输的位流用曼彻斯特编码。

- 以太网是基于冲突检测的总线复用方法,冲突退避算法是由硬件自动执行。

- 以太网传输的数据段的长度,DA + SA + TYPE + DATA + PAD最小为60B,最大为1514B。

- 通常的以太网卡可以接收3种地址的数据:广播地址、多播地址(或者叫组播地址,在嵌入式系统中很少用到)、自己的地址。但有时,用于网络分析和监控,网卡也可以设置为接收任何数据包。

- 任何两个网卡的物理地址都是不一样的,是世界上唯一的,网卡地址由专门机构分配。不同厂家使用不同地址段,同一厂家的任何两个网卡的地址也是唯一的。根据网卡的地址段(网卡地址的前3个字节)可以知道网卡的生产厂家。

8.6 以太网接口实现的方法

嵌入式处理器 + 网卡芯片。

- 把以太网芯片连接到嵌入式处理器的总线上。

- 通用性强,对嵌入式处理器没有特殊要求,不受处理器的限制,但是,嵌入式处理器和网络数据交换通过外部总线(通常是并行总线)交换数据,速度慢,可靠性不高,电路板走线复杂。

- 目前常见的以太网接口芯片,如CS8900、RTL8019/8029/8039、DM9008及DWL650无线网卡等。

带有以太网接口的嵌入式处理器。

- 常有以太网接口的嵌入式处理器通常是面向网络应用而设计的,要求嵌入式处理器有通用的网络接口(比如:MII接口)。

- 处理器和网络数据交换通过内部总线,速度快。

8.7 网络编程接口

BSD套接字(BSD Sockets)是使用的最广泛的网络程序编程方法。

- 主要用于应用程序的编写,用于网络上主机与主机之间的相互通信。

- 很多操作系统都支持BSD套接字编程。例如,UNIX、Linux、VxWorks、Windows的Winsock基本上是来自BSD Sockets。

套接字(Sockets)分为Stream Sockets和Data Sockets。

- Stream Sockets是可靠性的双向数据传输,对应使用TCP协议传输数据

- Data Sockets是不可靠连接,对应使用UDP协议传输数据

8.8 例题

略

9 CAN总线接口基本原理与结构

- CAN总线概述

- 在嵌入式处理器上扩展CAN总线接口

9.1 CAN总线概述

CAN(Controller Area Netword,控制器局域网)是德国Bosch公司于1983年为汽车应用而开发的,它是一种现场总线(FieldBus),能有效支持分布式控制和实时控制的串行通信网络。

- 1993年11月,ISO正式颁布了控制器局域网CAN国际标准(ISO11898)。

CAN总线是一种多主方式的串行通信总线。

- 理想的由CAN总线构成的单一网络中,是可以挂接任意多个节点,实际应用中节点数目受网络硬件的电气特性所限制。例如:当使用Philips P82C250作为CAN收发器时,同一网络中允许挂接110个节点。

- CAN总线具有很高的实时性能,已经在汽车工业、航空工业、工业控制、安全防护等领域中得到了广泛应用。

CAN总线的通信介质可采用双绞线、同轴电缆和光导纤维,最常用的是双绞线。

- 通信距离与波特率有关,最大通信距离可达10km,最大通信波特率可达1Mbps。

- CAN总线仲裁采用11位标识和非破坏性位仲裁总线结构机制,可以确定数据块的优先级,保证在网络节点冲突时最高优先级节点不需要冲突等待。

- CAN总线采用了多主竞争式总线结构,具有多主站运行和分散仲裁的串行总线以及广播通信的特点。

- CAN总线上任一节点可在任一时刻主动向网络上其他节点发送信息而不分主次,因此可在各节点之间实现自由通信。

CAN总线信号使用差分电压传送。

- 两条信号线被称为CAN_H和CAN_L,静态时均是2.5v左右,此时状态表示为逻辑1,也可以叫作“隐形”。

- 采用CAN_H比CAN_L高表示逻辑0,称为“显性”,通常电压值为CAN_H = 3.5v和CAN_L = 1.5v。

- 当“显性”位和“隐性”位同时发送的时候,最后总线数值降为“显性”。

- 这种特性为CAN总线的仲裁奠定了基础。

9.2 CAN总线接口

一些面向工业控制的嵌入式处理器集成了一个或者多个CAN总线控制器。

- 例如:Phillips公司的LPC2194和LPC2294(ARM7TDMI内核)带有4个CAN总线控制器。

- CAN总线控制器主要是完成时序控制逻辑转换等工作,要在电气特性上满足CAN总线标准,还需要一个CAN总线的物理层芯片,用它来实现TTL电平到CAN总线电平特性的转换,即CAN收发器。

实际上,多数嵌入式处理器都不带CAN总线控制器。

- 通常的解决方案是在嵌入式处理器的外部总线上扩展CAN总线接口芯片。

- 例如:Phillips公司的SJA1000 CAN总线接口芯片,Microchip公司的MCP251x系列(MCP2510和MCP2515)CAN总线接口芯片,这两种芯片都支持CAN2.0B标准。

- SJA 1000的总线采用的是地址线和数据线复用的方式,多数嵌入式处理器采用SJA 1000扩展CAN总线较为复杂。

9.3 嵌入式处理器上扩展CAN总线接口

MCP2510是由Microchip公司生产的CAN协议控制器,完全支持CAN总线V2.0A/B技术规范。

- 0~8字节的有效数据长度,支持远程帧

- 最大1Mb/s的可编程波特率

- 两个支持过滤波器(Filter,Mask)的接收缓冲区,三个发送缓冲区

- 支持回环(Loop Back)模式,便于测试

- SPI高速串行总线,最大5MHz

- 3v到5.5v供电

大多数嵌入式处理器都有SPI总线控制器,MCP2510可以3v到5.5v供电,能够直接和3.3v I/O口的嵌入式处理器连接,电路原理图如图所示。

MCP2510使用3.3v电压供电,可以直接和三星S3C44B0X处理器通过SPI总线连接。相关的资源如下。

- 使用一个扩展的I/O口(EXIO2)作为片选信号,电平有效。

- 用S3C2410A的外部中断6(EXINT6)作为中断管脚,低电平有效。

- 16MHz晶体作为输入时钟,MCP2510内部有晶振电路,用晶体可以直接起振使用TJA1050作为CAN总线收发器。

CAN总线收发器TJA1050必须使用5v供电。MCP2510和TJA1050连接的两个信号都是单向的信号。需要满足I/O口的电气特性。

- 从MCP2510输出的TXCAN信号是否满足TJA1050的输入电平。TJA1050位5v供电时,输入高电平 $V_{ih}$ 的范围是2~5.3v。而3.3v供电的MCP2510输出TXCAN信号高电平 $V_{oh}$ 最小值为2.6v,可以满足要求。

- 从TJA1050输出的RXD信号是否满足MCP2510的输入电平。3.3v供电的MCP2510输入信号RXCAN高电平范围 $V_{ih}$ :2~4.3v,无法满足5v逻辑的TJA1050输出电平,电阻分压实现单向电平转换。

分压电阻值的选择,需要考虑2个问题。

- TJA1050输出信号的驱动能力(输出电流 $\leq 15mA$ )

- MCP2510的RXCAN管脚的输入阻抗(输入电流 $\leq 5μA$ )

10 无线以太网基本原理与结构

- WLAN简介

- WLAN标准

10.1 WLAN简介

WLAN(Wireless Local Area Network,无线局域网)是利用无线通信技术在一定局部范围内建立的,是计算机网络与无线通信技术相结合的产物,以无线多址通道作为传输媒介,提供有线局域网的功能。

传输介质。

- 红外线IR

- 射频RF波段

10.2 WLAN标准

WLAN的标准:主要是针对物理层和媒质访问控制层(MAC层)。

- 涉及到所有使用的无线频率范围、控制接口通信协议等技术规范与技术标准。

11 IEEE 1394接口基本原理与结构

- IEEE 1394简介

- IEEE 1394的特点

- IEEE 1394的协议结构

11.1 IEEE 1394简介

IEEE 1394是Apple公司率先提出的一种高品质、高传输速率的串行总线技术,1995年被IEEE认定为串行工业总线标准。

- 1394作为一种标准总线,可以在不同的工业设备之间架起一座沟通的桥梁

- 在一条总线上可以接入63个设备

- 实时多媒体领域,大容量存储以及打印机、扫描仪上等等

- IEEE 1394规范仅支持64位固定解址模式

11.2 IEEE 1394的特点

支持多种总线速度,适应不同应用要求。

- IEEE 1394a:100Mb/s、200Mb/s、400Mb/s

- IEEE 1394b:800Mb/s、1600Mb/s、3200Mb/s

支持热插拔。

- 设备的资源均由总线控制器自动分配

- 总线控制器会自动重新配置好设备

接口有两种类型。

- 6针的六角形接口和4针的小型四角形接口

- 6针的六角形接口可向所连接的设备供电,而4针的四角形接口则不能

支持同步和异步两种传输方式。

- 设备可以根据需要动态地选择传输方式,总线自动完成带宽分配

- 要求实时传输并对数据的完整性要去不严格的场合,可采用同步传输方式

- 对数据完整性要求较高的场合,采用异步传输方式更好

支持点到点通信模式,IEEE 1394是多主总线。

- 每个设备均可以获取总线的控制权,与其他设备进行通信。

两种传输方式:Backplane模式和Cable模式。

- Backplane模式最小的速率也比USB1.1最高速率高,分别为12.5Mbps/s、25Mbps/s、50Mbps/s,可以用于多数的高带宽应用。

- Cable模式是速度非常快的模式,分为100Mbps/s、200Mbps/s和400Mbps/s几种,在200Mbps/s下可以传输不经压缩的高质量数据电影。

遵循ANSI IEEE 1212控制及状态寄存器(CSR)标准,定义了64位的地址空间。

- 可寻址1024条总线的63个节点,每个节点包含256TB的内存空间

支持较远距离的传输。

- 普通线缆:2个设备之间的最大距离可达4.5m(高级线缆可达15m)

- 玻璃光缆或5类双绞线:设备间距离可达100m以上。

支持公平仲裁原则,为每一种传输方式保证足够的传输带宽。

- 支持错误检测和处理。

六线电缆具有电源线,可传输8~40v的直流电压。

- 2对双绞线:信号传递

- 1对双绞线:供应电源

11.3 IEEE 1394的协议结构

IEEE 1394的协议栈由3层组成:物理层、链路层和事务层,另外还有一个管理层。

- 物理层和链路层由硬件构成,通常集成在同一块芯片上

- 事务层主要由软件实现

物理层提供IEEE1394的电气和机械接口,功能是重组字节流并将它们发送到目的节点上去。

- 物理层为链路层提供服务

- 解析字节流并发送数据包给链路层

链路层提供了给事务层确认的数据服务,包括:寻址、数据组帧和数据校验。

- 提供直接面向应用的服务

- 支持同步和异步传输模式

- 链路层的底层提供了仲裁机制

11.4 例题

- IEEE 1394具有(D)位地址空间,IEEE 1394的通信协议具有三个协议包,不包括(B)。

(1)

A. 8

B. 16

C. 32

D. 64

(2)

A. 事物层

B. 表示层

C. 链路层

D. 物理层

12 总线分类

| 总线分类 | 说明 | 常用总线 |

|---|---|---|

| 内部总线 | 内部总线是微处理机内部各外围芯片与处理器之间的总线,用于芯片一级的互连 | IIC总线、SPI总线、SCI总线等 |

| 系统总线 | 系统总线是微机中各插件板与系统板之间的总线,用于插件板一级的互连 | ISA总线、EISA总线、VESA总线、PCI总线等 |

| 外部总线 | 外部总线则是微机和外部设备之间的总线,微机作为一种设备,通过该总线和其他设备进行信息与数据交换,它用于设备一级的互连 | RS232、RS485、USB总线、IEEE1394总线等 |

12.1 例题

- 以下关于嵌入式系统总线的描述中,不正确的是(C)。

A. 异步通信时数据是一帧一帧传送的,没帧数据的传送靠起始位来同步

B. SPI、IIC、UART都属于串行通信方式

C. 同步通信方式是字符同步,且在字符与字符之间的时序仍然是同步的

D. RS232、RS485、USB、IEEE1394总线都属于外部总线

- 不属于系统总线的是(C)。

A. ISA

B. EISA

C. SCSI

D. PCI

2.2.3 全双工

全双工通信:数据可以在同一时刻从设备A传输到设备B,或从设备B传输到设备A,即可以同时双向传输。如电话。

第十四章——嵌入式系统总线和通讯接口

前言:

计算机第十四章节主要知识点。

1 知识点介绍

- 串行接口基本原理与结构

- 并行接口基本原理与结构

- PCI接口基本原理与结构

- USB接口基本原理与结构

- SPI接口基本原理与结构

- IIC接口基本原理与结构

- 网络接口基本原理与结构

- 总线分类

2 串行接口基本原理与结构

- 串行通信概述

- RS-232C串行接口

- RS-422串行通信接口

- RS-485串行总线接口

2.1 串行通信概述

串行通信:数据是一位一位地进行传输的,在传输中每一位数据都占据一个固定的时间长度。

优点。

- 传输线少、成本低

- 特别适合远距离传送

缺点。

- 速度慢

2.2 串行通信模式

2.2.1 单工

串行数据传送有3种基本的通信模式:单工、半双工、全双工通信。

单工通信:数据仅能从设备A到设备B进行单一方向的传输。如遥控、遥测等。

2.2.2 半双工

半双工通信:数据可以从设备A到设备B进行传输,也可以从设备B到设备A进行传输,但不能在同一时刻进行双向传输。如:对讲机。

2.2.3 全双工

全双工通信:数据可以在同一时刻从设备A传输到设备B,或从设备B传输到设备A,即可以同时双向传输。如电话。

2.2.4 串行通信异步

串行通信在信息格式上可以分为:异步通信和同步通信方式。

异步通信方式。

- 是指通信的发送与接收设备使用各自的时钟,控制数据的发送和接收过程。

- 为使双方的收发协调,要求发送和接收设备的时钟尽可能一致。

异步通信方式。

- 数据是一帧一帧传送的,没帧数据包含有起始位(“0”)、数据位、奇偶校验位和停止位(“1”),每帧数据的传送靠起始位来同步。

- 一帧数据的各位代码间的时间间隔是固定的,而相邻两帧的数据其时间间隔是不固定的。

- 在异步通信的数据传送中,传输线上允许空字符。

字符格式。

- 异步通信对字符格式、波特率、校验位有确定的要求。

字符格式。

- 每个字符传送时,必须前面加一位起始位,后面加上1、1.5或2位停止位。

- 例如ASCII码传送时,一帧数据的组成是:前面1个起始位,接着7位ASCII编码,再接着一位奇偶校验位,最后一位停止位,共10位。

2.2.5 波特率和校验位

波特率。

- 传送数据位的速率称为波特率,用位/秒(bit/s)来表示,称之为波特。

- 例如,数据传送的速率为120字符/秒,每帧包括10个数据位,则传送波特率为: $10 \times 120 = 1200b/s = 1200波特$

- 异步通信的波特率的数值通常为:150、300、600、1200、2400、4800、9600、14400、28800等,数值成倍数变化。

校验位。

- 偶校验就是要使字符加上校验位有偶数个“1”。

- 奇校验就是要使字符加上校验位有奇数个“1”。

- 例如数据“00010011”,共有奇数个“1”,偶校验时,则校验位就置为“1”,奇校验时,则校验位就置为“0”。

2.2.6 串行异步特点

异步通信的特点。

- 不要求收发双方时钟的严格一致,实现容易,设备开销较小。

- 但每个字符要附加2~3位用于起始,各帧之间还有间隔,因此传输效率不高。实际使用率只有约80%。

2.2.7 串行通信同步

同步通信。

- 是一种比特同步通信技术,要求收发双方具有同频同相的同步时钟信号,只需在传送报文的最前面附加特定的同步字符,使收发双方建立同步,此后便在同步时钟的控制下逐位发送/接收。

- 同步传输采用字符块的方式,减少每一个字符的控制和错误检测数据位,因而可以具有较高的传输速率。

- 即将许多字符聚集成一字符块后,在每块信息之前要加上1~2个同步字符,字符块之后再加入适当的错误检测数据才传送出去。

特点。

- 数据传输速率较高。

- 但要求发送方时钟和接收方时钟保持严格同步。

2.2.8 串口同步和异步发送

2.3 RS-232C串行接口

2.3.1 接口规格

RS-232C是美国电子工业协会(EIA)制定的一种串行通信接口标准。

RS-232C接口规格。

- EIA所制定的传送电气规格如下表所示。

- RS-232C通常以±12v的电压来驱动信号线,TTL标准与RS-232C标准之间的电平转换电路通常采用集成电路芯片实现,如M2AX23等。

| 状态 | L(Low) | H(Hight) |

|---|---|---|

| 电压范围 | -25~-3v | +3v~25v |

| 负逻辑 | 1 | 0 |

2.3.2 接口信号

EIA制定的RS-232C接口与外界的相连采用25芯(DB-25)和9芯(DB-9)D型插接件,实际应用中,并不是每只引脚信号都必须用到。

2.3.3 引脚功能

RS-232C DB-9各引脚功能如下。

| 引脚号 | 符号表示 | 名称 | 说明 |

|---|---|---|---|

| 1 | CD | 载波检测 | 主要用于Modem通知计算机其处于在线状态,即Modem检测到拨号音 |

| 2 | RXD | 接收数据线 | 用于接收外部设备送来的数据 |

| 3 | TXD | 发送数据线 | 用于将计算机的数据发送给外部设备 |

| 4 | DTR | 数据终端 | 当次引脚高电平时,通知Modem可以进行数据传输,计算机已经准备好 |

| 5 | SG | 信号地 | |

| 6 | DSR | 数据设备就绪 | 此引脚为高电平时,通知计算机Modem已经准备好,可以进行数据通信 |

| 7 | RTS | 请求发送 | 此引脚由计算机来控制,用以通知Modem马上传送数据至计算机,否则Modem将收到的数据暂时放入缓冲区中 |

| 8 | CTS | 允许发送 | 此引脚由Modem控制,用以通知计算机将要传送的数据送至Modem |

| 9 | RI | 振铃提示 | Modem通知计算机有呼叫进来,是否接听呼叫由计算机决定 |

2.3.4 连接方式

RS-232C的基本连接方式。

- 计算机利用RS-232C接口进行串口通信,有简单连接和完全连接两种连接方式

- 简单连接又称三线连接,即只连接发送数据线、接收数据线和信号地,实现全双工通信

- 如果应用中还需要使用RS-232C的控制信号,则采用完全连接方式。

2.4 RS-422串行接口

RS-422标准是RS-232的改进型,是一种可单机发送多机接收的平衡传输规范,传输速率可达10Mb/s。采用差分传输方式,也称平衡传输。

- 允许在相同传输线上连接多个接收节点,最多可接10个节点,即一个主设备(Master),其余10个为从设备(Slave),从设备之间不能通信。

- 支持一点对多点的双向通信。RS-422四线接口由于采用单独的发送和接收通道,因此不必控制数据方向,各装置之间任何必须的信号交换均可以按软件方式(XON/XOFF握手)或硬件方式(一对单独的双绞线)实现。

RS-422的最大传输距离为4000英尺(约1219m),最大传输速率为10Mb/s。

- 传输速率与平衡双绞线的长度有关,只有在很短的距离下才能获得最高传输速率

- 在最大传输距离时,传输速率为100kb/s

- 一般100m长的双绞线上所能获得的最大传输速率仅为1Mb/s

RS-422需要在传输电缆的最远端连接一个电阻,要求电阻阻值约等于传输电缆的特性阻抗。

- 在短距离(300m以下)传输时可以不连接电阻。

2.5 RS-485串行接口

在RS-422的基础上,为扩展应用范围,EIA制定了RS-485标准,增加了多点、双向通信能力。

- 在通信距离为几十米至上千米时,通常采用RS-485接收器

- RS-485接收器采用平衡发送和差分接收

- 即在发送端,驱动器将TTL电平信号转换成差分信号输出,在接收端,接收器将差分信号变成TTL电平,因此具有抑制共模干扰的能力。

- 接收器能够检测低达200mv的电压,具有高的灵敏度,故数据传输距离可达千米以上。

RS-485可以采用二线与四线方式,二线制可以实现真正的多点双向通信。

- 采用四线连接时,与RS-422一样只能实现点对点的通信,即只能有一个主设备,其余为从设备。

- RS-485可以连接多达32个设备

RS-485的共模输出电压在-7~+12v之间,接收器最小输入阻抗为12kΩ。

RS-485满足所有RS-422的规范,所以RS-485的驱动器可以在RS-422网络中应用。

RS-485的最大传输速率为10Mb/s。在最大传输距离时,传输速率为100kb/s。

RS-485需要两个终端电阻,接在传输总线的两端,要求电阻阻值约等于传输电缆的特性阻抗。

- 在短距离传输(在300m以下)时可不需终端电阻。

2.6 例题

- 使用串行总线传输数据时,被传输的数据(D)。

A. 在发送设备和接收设备中都是进行串行到并行的变换

B. 在发送设备和接收设备中都是进行并行到串行的变换

C. 在发送设备中进行串行到并行的变换,接收设备中进行并行到串行的变换

D. 在发送设备中进行并行到串行的变换,接收设备中进行串行到并行的变换

3 并行接口基本原理与结构

- 并行接口分类

- 并行总线

3.1 并行接口基本概念

并行通信通常是将数据字节的各位用多条数据线同时进行传送。

- 一般用来连接打印机、扫描仪等,所以又称打印口。

特定。

- 控制简单,传输速度快

- 由于传输线较多,长距离传送时成本高且接收方的各位同时接收存在的困难。

3.2 并行接口分类

并行接口可以分为。

- SPP(标准并口)

- EPP(增强型并口)

- ECP(扩展型并口)

3.3 并行总线分类

&emsep; 并行总线分为。

- 标准并行总线

- 非标准并行总线

常用的并行标准总线:IEEE488总线和SCSI总线。

总线是一种高性能非标准的通用多用户并行总线。

3.4 并行总线IEE488

IEEE488总线。

- 又称GPIB总线(General Purpose Interface Bus,通用接口总线)

- 位并行、字节串行双向异步方式传输信号

- 总线方式连接,仪器设备直接并联于总线上,总线上最多可连接15台设备

- 最大传输距离为20m,信号传输速度一般为500kb/s,最大传输速度为1Mb/s

- 广泛应用在仪器、仪表、测控领域

3.5 并行总线SCSI和MXI

SCSI(Small Computer System Interface,小型计算机系统接口)总线。

- 速度可达5Mb/s,传输距离6m

- 传输速率很高

- 普通用作计算机的高速外设总线,如连接高速硬盘驱动器

MXI总线(Multi-system Extension Interface bus,多系统扩展接口总线)。

- 是一种高性能非标准的通用多用户并行总线

- 32位高速并行总线

- 最高速度可达23Mb/s,传输距离20m

- 用作计算机与测控机箱的互连

3.6 例题

- 串行总线与并行总线比,(C)。

A. 串行总线成本高,速度快

B. 串行总线成本高,速度慢

C. 并行总线成本高,速度快

D. 并行总线成本低,速度快

- 信息可以在两个方向上同时传输的总线属于(C)。

A. 单工总线

B. 半双工总线

C. 全双工总线

D. 单向总线

- 以下关于总线的叙述中,不正确的是(C)。

A. 并行总线适合近距离高速数据传输

B. 串行总线适合长距离数据传输

C. 单总线结构在一个总线上适合不同种类的设备,设计简单且性能很高

D. 专用总线在设计上可以与连接设备实现最佳匹配

4 PCI接口基本原理与结构

- PCI接口基本结构

4.1 PCI接口基本结构

PCI(Peripheral Component Interconnect,外围设备互连)总线是由Intel公司推出的一种局部总线,是当前用于系统扩展最流行的总线之一。

PCI总线是地址、数据多路复用的高性能32位和64位总线,是微处理器与外围控制部件、外围附加板之间的互连机构。

PCI定义了32位数据总线,并且可扩展为64位。总线速度有32MHz和66MHz两种。

- 改良的PCI系统PCI-X,数据传输速度最高可以达到64位@133MHz

- PCI总线主板插槽的体积比ISA总线插槽小,支持突发读写操作(突发数据传输),可同时支持多组外围设备

与ISA总线不同,PCI总线的地址总线与数据总线是分时复用的,支持即插即用(PNP:Plug-and-Play)、中断共享等功能。

PCI总线在数据传输时,由一个PCI设备做发起者(称为Master、Initator),而另一个PCI设备做目标(称为Slave、Target)。

- 总线上所有时序的产生与控制都由Master发起

- PCI总线在同一时刻只能供一对设备完成传输,要求有一个仲裁机构来决定谁有权拿到总线的主控权

4.1.1 例题

- 关于PCI总线,下列说法不正确的是(A)。

A. PCI总线是地址、数据多路复用的一种总线,不支持即插即用,支持中断共享功能

B. PCI定义了32位数据总线,也可扩展为64位总线

C. PCI总线在数据传输时,由一个PCI设备做发起者,而另一个PCI设备做目标

D. PCI总线要求有一个仲裁机构来决定谁有权拿到总线的主控权,所以在同一时刻只能供一对设备完成传输

- 在以下描述中PCI总线的基本概念中,正确的表述有(B)、(E)、(F)、(G)、(J)、(K)。

A. PCI总线是一个与处理器有关的高速外围总线

B. PCI总线的基本传输机制是触发传输

C. PCI设备一定是主设备

D. PCI的物理地址与其他总线一样,是由内存地址空间和I/O地址组成

E. PCI设备的地址译码不能对配置空间直接寻址

F. PCI设备识别主要是对开发商代码和设备代码进行识别

G. 访问配置空间时,PCI桥应提供IDSEL信号以选择PCI设备

H. 系统中只允许有一条PCI总线

I. PCI总线是高速串行总线

J. PCI总线有3种桥,即HOST/PCI桥,PCI/PCI桥,PCI/LEGACY桥

K. PCI桥是可以把一条总线的地址空间映射到另一条总线的地址空间

5 USB接口基本原理与结构

- USB总线的主要性能特点

- 物理接口

USB(Universal Serial Bus,通用串行总线)是由Compaq、HP、Intel、Lucent、Microsoft、NEC和Philips公司制定的连接计算机与外围设备的机外串行总线。

- 最多可连接127个设备

- 用于多种嵌入式系统设备的数据通信。如移动硬盘、PDA

5.1 热插拔

USB提供机箱外的热插拔功能,连接外设不必再打开机箱,也不必关闭主机电源,USB可智能地识别USB链上外围设备的动态插入或拆除,具有自动配置和重新配置外设的能力,连接设备方便,使用简单。

可连接多个外部设备。

- 每个USB系统中有1个主机,USB总线采用“级联”方式可连续多个外部设备。

- 每个USB设备用一个USB插头连接到上一个USB设备的USB插座上,而其本身又提供一或多个USB插座供一下一个或多个USB设备连接使用。

- 这种多重连接是通过集线器(Hub)来实现的,整个USB网络中最多可连接127个设备,支持多个设备同时操作

5.2 USB总线的主要性能特点

可同时支持不同同步传输方式和速率的设备。

- 可同时支持同步传输和异步传输两种传输方式

- 可同时支持不同速率的设备,速率最高可达几百Mb/s

- 支持主机与设备之间的多数据流和多消息流传输,且支持同步和异步传输类型

- 提供了四种不同的数据传输类型:控制传输、数据传输、中断数据传输和同步数据传输

较强的纠错能力。

- USB系统可实时地管理设备插拔

- 在USB协议中包括了传输错误管理、错误恢复等功能,同时根据不同的传输类型来处理传输错误

低成本的电缆和连接器。

- USB采用统一的4引脚插头和一根四芯的电缆传送信号和电源

- 电缆长度可达5m

总线供电。

- USB总线可以为连接在其上的设备提供5v电压/100mA电流的供电,最大可提供500mA的电流

- USB设备也可采用自供电方式,可以通过电池或其他的电力设备

- 支持节约能源的挂机和唤醒模式

5.3 USB总线的应用

5.4 USB总线物理接口

USB总线的电缆有一对标准尺寸的双绞信号线和一对标准尺寸的电源线,共4根导线。

| 连接序号 | 信号名称 | 典型连接线 |

|---|---|---|

| 1 | VBUS(USB电源) | 红 |

| 2 | D+(正差分信号) | 白 |

| 3 | D-(负差分信号) | 绿 |

| 4 | GND(USB地) | 黑 |

| 外层 | 屏蔽层 | - |

5.5 例题

- 下面关于通用串行总线USB的描述,不正确的是(D)。

A. USB接口为外设提供电源

B. USB设备可以起集线器作用

C. 可同时连接127台输入/输出设备

D. 通用串行总线不需要软件控制就能正常工作

- 在嵌入式系统设计中,用来进行系统初始代码调试的接口称为(D)。

A. PCI接口

B. USB接口

C. 网络接口

D. JTAG接口

6 SPI接口基本原理与结构

- SPI接口简介

- SPI接口基本原理

- SPI接口工作模式

6.1 SPI接口简介

SPI(Serial Peripheral Interface,串行外围设备接口)是由Motorola公司开发的一个低成本、易使用的接口,主要用在微处理器(MCU)和外围设备芯片之间进行连接。

- SPI接口可以用来连接存储器、AD转换器、DA转换器、实时时钟日历、LCD驱动器、传感器、音频芯片,其他处理器等。

SPI是一个4线接口,主要使用4个信号。

- 主机输出/从机输入(MOSI)

- 主机输入/从机输出(MISO)

- 串行SCLK或SCK

- 外设片选( $\overline{\text{CS}}$ )

- 有些处理器有SPI接口专用的芯片选择,称为从机选择( $\overline{\text{SS}}$ )

MOSI信号由主机产生,从机接收。

- 在有些芯片上,MOSI只被简单的标为串行输入(SI),或者串行数据输入(SDI)。

MISO信号由主机产生,不过还是在主机的控制下产生的。

- 在一些芯片上,MISO有时被称为串行输出(SO)或串行数据输出(SDO)。

外设片选信号:通常只是由主机的备用I/O引脚产生的。

与标准的串行接口不同,SPI是一个同步协议接口,所有的传输都参照一个共同的时钟,这个同步时钟信号由主机(处理器)产生,接收数据的外设(从设备)使用时钟来对串行比特流的接收进行同步化。

- 可以将多个具有SPI接口的芯片连到主机的同一个SPI接口上,主机通过控制从设备的片选输入引脚来选择接收数据的从设备。

6.2 SPI接口基本原理

如图所示,微处理器通过SPI接口与外设进行连接。

- 主机和外设都包含一个串行移位寄存器,主机写入一个字节到它的SPI串行寄存器,SPI寄存器通过MOSI信号线将字节传送给外设。

- 外设也可以将自己移位寄存器中的内容通过MISO信号线传送到主机。主机和外设的两个移位寄存器中的内容被互相交换。

- 外设的写操作和读操作是同步完成的,因此SPI成为一个很有效的协议。

如果只是进行写操作,主机只需忽略收到的字节。

如果主机要读取外设的一个字节,就必须发送一个空字节来触发从机的数据传输。

当主机发送一个连续的数据流时,有些外设能进行多字节传输。

- 如多数具有SPI接口的存储器芯片都以这种方式工作。在这种传输方式下,SPI外设的芯片选择端必须在整个传输过程中保持低电平。

- 如,存储器芯片会希望在一个“写”命令之后紧接着收到的是4个地址字节(起始地址),这样后面接收到的数据就可以存储到该地址。

其他外设只需要一个单字节(比如一个发给AD转换器的命令),有些甚至还支持菊花链连接,如图所示。

- 主机处理器从其SPI接口发送3个字节的数据

- 第1个字节发送给外设A,当第2个字节发送给外设A的时候,第1个字节已移出了A,而传送给了B

- 同样,主机想要从外设A读取一个结果,它必须要再发送一个3字节(空字节)的序列,这样就可以把A中的数据移到B中,然后再移到C中,最后送回到主机。在这个过程中,主机还依次从B和C接收到字节。

注意,菊花链连接不一定适用于所有的SPI设备,特别是要求多字节传输的(比如存储器芯片)设备。有的外设西片不支持菊花链连接。

6.3 SPI接口工作模式

根据时钟极性和时钟相位的不同,SPI有4种工作模式。

- 时钟极性有高电平、低电平两种

- 时钟相位有两个:时钟相位0和时钟相位1

时钟极性(CPOL:Clock Polarity)。

- 时钟极性为低电平时:空闲时时钟(SCK)处于低电平,传输时跳转到高电平

- 时钟极性为高电平时:空闲时时钟(SCK)处于高电平,传输时跳转到低电平

时钟相位(CPHA:Clock Phase)。

- 当CPHA为0时,时钟周期的前一边缘采集数据

- 当CPHA为1时,时钟周期的后一边缘采集数据

四种工作模式下的SCLK表现如下。

- 红线表示采集数据,下面的一个例子是S3C2440上面SPI控制器的总线范例。

6.4 例题

- 以下四种串行总线中,一组总线上不能挂连多个器件的是(A)。

A. RS232

B. RS485

C. $I^2C$

D. SPI

7 IIC接口基本原理与结构

- IIC接口简介

- IIC总线的数据传送

- IIC总线工作原理

IIC Bus(Inter Integrated Circuit BUS,内部集成电路总线)是由Philips公司推出的二线制串行扩展总线,用于连接微控制器及其外围设备。

- IIC总线是具备总线仲裁和高低速设备同步等功能的高性能多主机总线

- 直接用导线连接设备,通信时无需片选信号

- IIC总线的协议层包括物理层和数据链路层。物理层有两根信号线,在链路层每个连接到IIC总线上的设备都有唯一的地址

7.1 IIC接口简介

在IIC总线上,物理层只需要两条线一串行数数据SDA线、串行时钟SCL线,它们用于总线上器件之间的信息传递。

- SDA和SCL都是双向的

- 每个器件都有一个唯一的地址以供识别,而且各器件都可以作为一个发送器或接收器(由器件的功能决定的)。

7.2 操作模式

IIC总线有4中操作模式。

- 主发送模式

- 主接收模式

- 从发送模式

- 从接收模式

7.3 启动信号

IIC总线的启动信号。

- 当IIC接口处于从模式时,要想数据传输,必须检测SDA线上的启动信号,启动信号由主器件产生

- 在SCL信号为高时,SDA产生一个由高变低的电平变化,即产生一个启动信号

- 当IIC总线上产生了启动信号后,那么这条总线就被发出启动信号的主器件占用了,变成”忙“状态

7.4 读写数据

主器件产生一个启动信号后,会立即送出一个从地址,用来通知将与它进行数据通信的从器件。

- 1个字节的地址包括7位的地址信息和1位的传输方向指示位(R/W)

- 如果第7位为“0”,表示主机发送数据(W),即进行一个写操作

- 如果“1”,表示主机接收数据(R),即进行一个读操作

7.5 数据传输格式

数据传输格式。

- SDA线上传输的每个字节长度都是8位,每次传输中字节的数量是没有限制的。

- 在起始条件后面的第一个字节是地址域,之后每个传输的字节后面都有一个应答(ACK)位(即一帧共有9位)

- 传输中串行数据的MSB(字节的高位)首先发送

7.6 应答信号

应答信号。

- 为了完成1个字节的传输操作,接收器应该在接收完1个字节之后发送ACK位到发送器,告诉发送器,已经收到了这个字节。

- ACK脉冲信号在SCL线上第9个时钟处发出(前面8个时钟完成1个字节的数据传输,SCL上的时钟都是由主器件产生的)。

- 当发送器要接收ACK脉冲时,应该释放SDA信号线,即将SDA置高。

- 接收器在接收完前面的8位数据后,将SDA拉低。

- 发送器探测到SDA为低,就认为接收器成功接收了前面的8位数据。

7.7 IIC总线工作原理

总线竞争的仲裁。

- IIC总线上可以挂接有多个器件,有时会发生两个或多个主器件同时想占用总线的情况

- IIC总线具有多主控制能力可对发生在SDA线上的总线竞争进行仲裁

- 仲裁原则:当多个主器件同时想占用总线时,如果某个器件发送高电平,而另一个主器件发送低电平,则发送电平与此时SDA总线电平不符的那个器件将自动关闭其输出级

总线竞争的仲裁在两个层次上进行的。

- 首先是地址位的比较,如果主器件寻址同一个从器件,则进入数据位的比较,从而确保了竞争仲裁的可靠性

- 由于是利用IIC总线上的信息进行仲裁,不会造成信息的丢失

IIC总线的数据传输过程。

- 开始:主设备产生启动信号,表明数据传输开始。

- 地址:主设备发送地址信息,包含7位的从设备地址和1位的数据方位指示位(读或写位,表示数据流的方向)。

- 数据:数据指示位,数据在主设备和从设备之间进行传输。数据一般以8位传输,MSB先传;具体能传输多少量的数据并没有限制。接收器产生1位的ACK(应答信号)表明收到了每个字节。传输过程可以被中止和重新开始。

- 停止:注射别产生停止信号,结束数据传输。

7.8 例题

- 关于IIC总线,下列说法错误的是(B)。

A. IIC总线有4种操作模式:主发送模式、主接收模式、从发送模式和从接收模式

B. 传输中串行数据的LSB首先发送

C. IIC总线的数据传输过程包括了开始、地址、数据和停止信号的产生

D. IIC总线上,只需要两条线——串行数据SDA线、串行时钟SCL线,它们用于总线上器件之间的信息传递,并且都是双向的

- IIC总线协议包含物理层和数据链路层,下图是常见的多个IIC设备接口示意图,下面描述不正确的是()。

A. 在物理层,IIC使用两条信号线,一条是串行数据线,一条是串行时钟线

B. 在数据链路层,每个IIC设备不用具有唯一的设备地址

C. 在IIC构成系统中,可以多主系统,但任一时刻只能有一个主IIC设备

D. IIC具有总线仲裁功能

8 网络接口

- 以太网接口基本原理与结构

- CAN总线接口基本原理与结构

- 无线以太网基本原理与结构

- 1394接口基本原理与结构

8.1 以太网接口基本原理与结构

- 以太网基础知识

- 嵌入式以太网接口的实现方法

- 网络编程接口

8.2 以太网基础知识

以太网(Ethernet)是目前应用最广泛的局域网通讯方式,同时也是一种协议。

以太网协议定义了一系列软件和硬件标准,从而将不同的设备连接在一起。

嵌入式系统通常使用的以太网协议是IEEE802.3协议。

- 以太网接口电路主要由媒质接入控制MAC控制器和物理层接口(Physical Layer,PHY)两大部分构成

8.3 传输编码

在802.3版本的标准中,没有采用直接的二进制编码(即用0v表示“0”,用5v表示“1”),而是采用。

- 曼彻斯特编码(Manchester Encoding)

- 差分曼彻斯特编码(Differential Manchester Encoding)

曼彻斯特编码的规律。

- 每位中间有一个电平跳变,从高到低的跳变表示“0”,从低到高的跳变表示”1“。

差分曼彻斯特编码的规律。

- 每位的中间有一个电平跳变,但不用这个跳变来表示数据,而是利用每个码元开始有无跳变来表示“0”或“1”,有跳变表示“0”,无跳变表示“1”(保持性)。

曼彻斯特编码和差分曼彻斯特编码相比,前者编码简单,后者能提供更好的噪声抑制性能。

- 在802.3系统中,采用曼彻斯特编码,其高电平为+0.85v,低电平信号为-0.85v,这样指令信号电压仍然是0v。

8.4 802.3Mac层的帧

802.3 Mac层的以太网的物理传输帧如表所示。

| PR | SD | DA | SA | TYPE | DATA | PAD | FCS |

|---|---|---|---|---|---|---|---|

| 56位 | 8位 | 48位 | 48位 | 16位 | 不超过1500字节 | 可选 | 32位 |

- PR:同步位,用于收发双方的时钟同步,同时也指明了传输的速率,是56位的二进制数101010101010…,最后2位是10。

- SD:分隔位,表示下面跟着的是真正的数据而不是同步时钟,为8位的10101011。

- DA:目的地址,以太网的地址为48位二进制地址,表明该帧传输给哪个网卡。如果为FFFFFFFFFFFF,是广播地址。广播地址的数据可以被任何网卡接收到。

- SA:源地址,48位,表明该帧的数据是哪个网卡发的,即发送端的网卡地址,是6个字节。

- TYPE:类型字段,表明该帧的数据是什么类型的数据,不同协议的类型字段不同。如:0800H表示数据为IP包,0806H表示数据为ARP包,814CH是SNMP包,8137H为IPX/SPX包。

- DATA:数据段,该段数据不能超过1500B,以太网规定整个传输包的最大长度不能超过1514B(14B为DA,SA,TYPE)。

- PAD:填充位。以太网帧传输的数据包最小不能小于60B,(除去DA、SA、TYPE的14B),还必须传输46B的数据,当数据段的数据不足46B时,后面通常是补0(也可以补其他值)。

- FCS:32位数据校验位。32位的CRC校验,该校验由网卡自动计算,自动生成,自动校验,自动在数据段后面填入。不需要软件管理。

PR、SD、PAD、FCS数据段是网卡(包括物理层和Mac层的处理)层自动产生的,剩下的DA、SA、TYPE、DATA4个段的内容由上层软件控制。

8.5 以太网数据传输的特点

以太网数据传输的特点。

- 所有数据位的传输由低位开始,传输的位流用曼彻斯特编码。

- 以太网是基于冲突检测的总线复用方法,冲突退避算法是由硬件自动执行。