第十一章——嵌入式微处理器基础

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

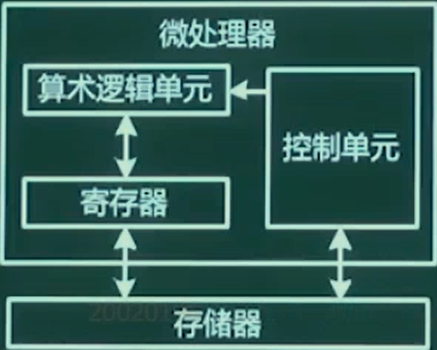

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

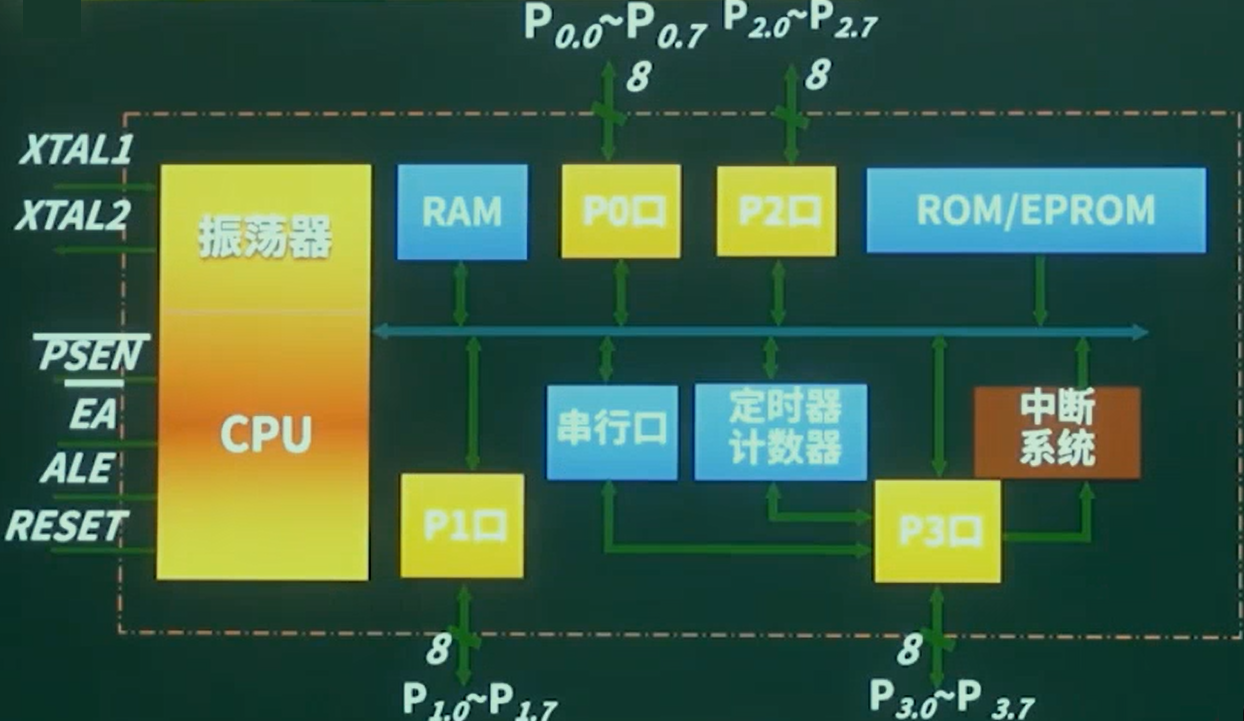

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

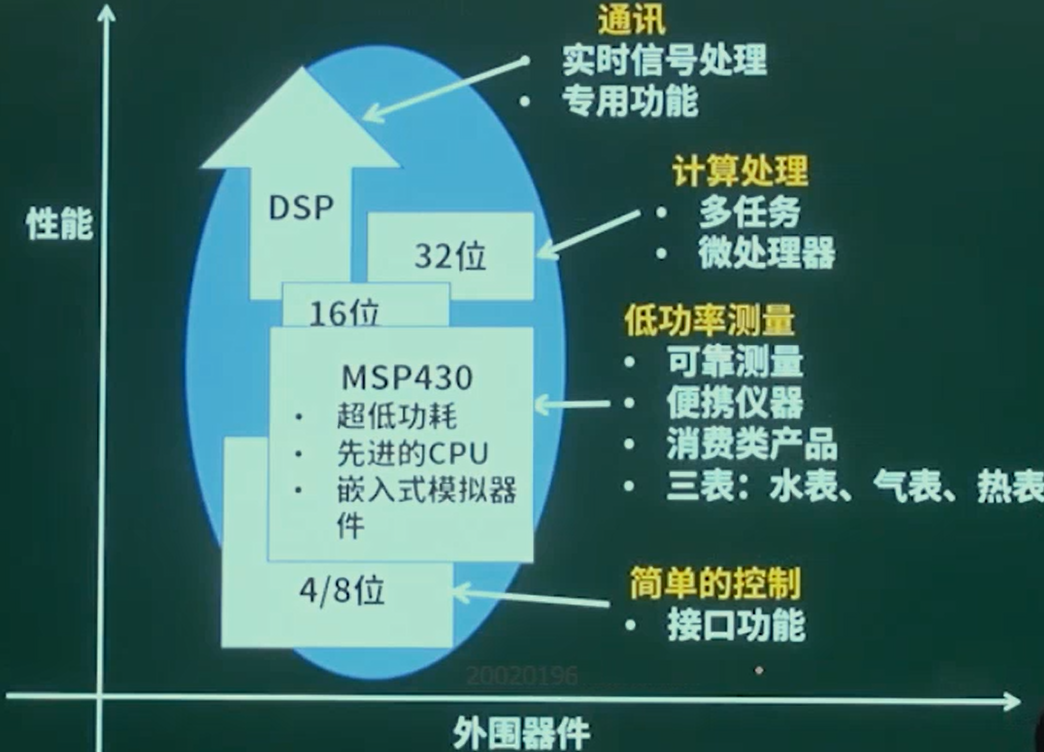

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

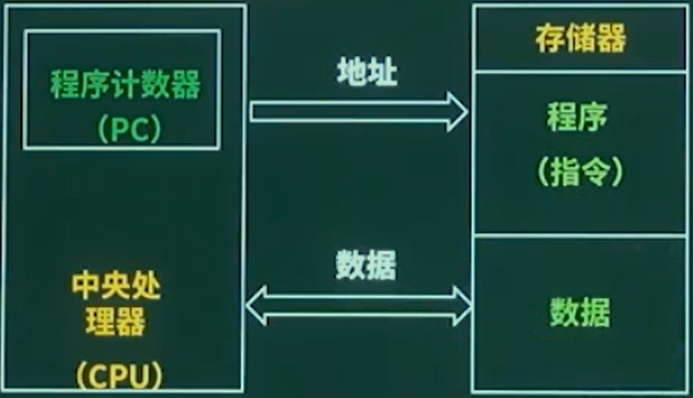

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

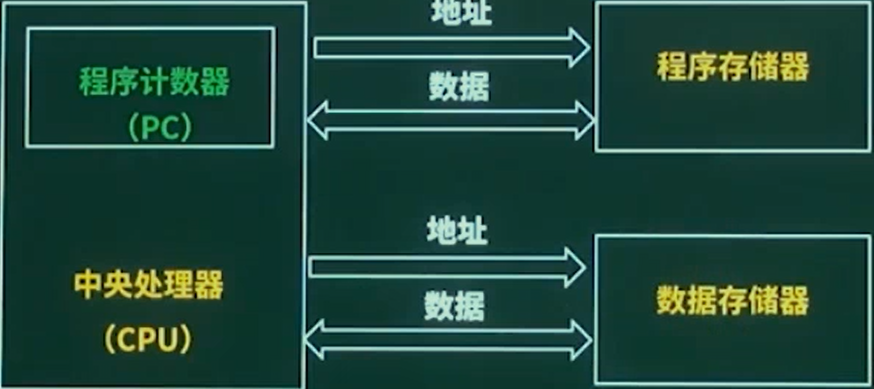

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;

2.5 Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能 至少是不实际 |

目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

2.6 例题

- Flynn分类基于信息流特征将计算机分成4类,其中()只有理论意义而无实例(B)。

A. SISD

B. MISD

C. SIMD

D. MIMI

2.7 CISC与RISC

- 复杂指令集计算机(CISC)

- 精简指令集计算机(RISC)

- 尽管RISC体系与CISC体系相比较有较多的优点,但RISC和CISC各有优势。如超长指令集。

| 序号 | 类别 | CISC | RISC |

| 1 | 指令系统 | 指令数量很多 | 较少,通常少于100 |

| 2 | 执行时间 | 有些指令执行时间很长 | 没有较长执行时间的指令 |

| 3 | 编码长度 | 编码长度可变 | 编码长度固定 |

| 4 | 寻址方式 | 寻址方式多样 | 简单寻址 |

| 5 | 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器进行算术和逻辑操作 |

| 6 | 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术 |

- 超流水线

- 超标量

- 超长指令字

2.7.1 例题

- 嵌入式处理器指令系统一般采用精简指令集(RISC)或者复杂指令集(CISC),下列关于RISC和CISC描述错误的是(C)。

A. CISC的指令种类要多于RISC

B. RISC的寻址方式复杂,CISC的寻址方式简单

C. CISC的有些指令执行时间长,RISC多为单周期指令

D. RISC中的Load/Store指令对存储器进行操作

2.8 常用嵌入式微处理器介绍

- 8位微处理器

- 16位微处理器

- 32位微处理器

- 多核处理器

3 8位处理器

8位微处理器:是指使用8位数据总线的微处理器

- 8位处理器是指使用8位数据总线的微处理器,大部分8位微处理器有16位的地址总线。

- CISC,哈佛架构。

- 具有低成本、可靠性高、可扩充内存及接口设备等特点。

- 但功能、性能和片上资源相对16位/32位/64位嵌入式微控制器来讲也较简单。

常见型号包括

- Intel的MCS-51系列

- Fairchild及Mostek公司的3870系列

3.1 MCS-51

- I/O口线:P0、P1、P2、P3

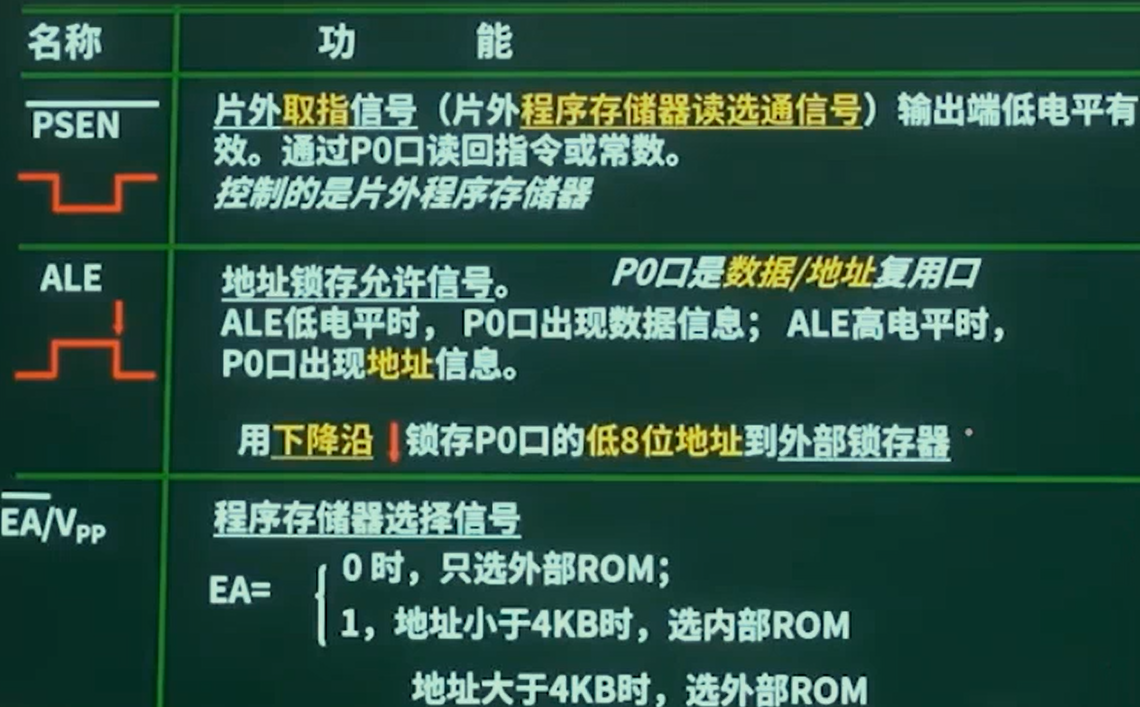

- 控制口线: $\overline{\text{PSEN}}$ 、ALE、 $\overline{\text{EA}}$ /VPP、RESET

- 电源:Vcc(+5v)、GND

- 时钟:XTAL1(片内震荡电路输入端)、XTAL2(片内振荡电路输出端)

3.2 引脚说明

3.3 时钟电路

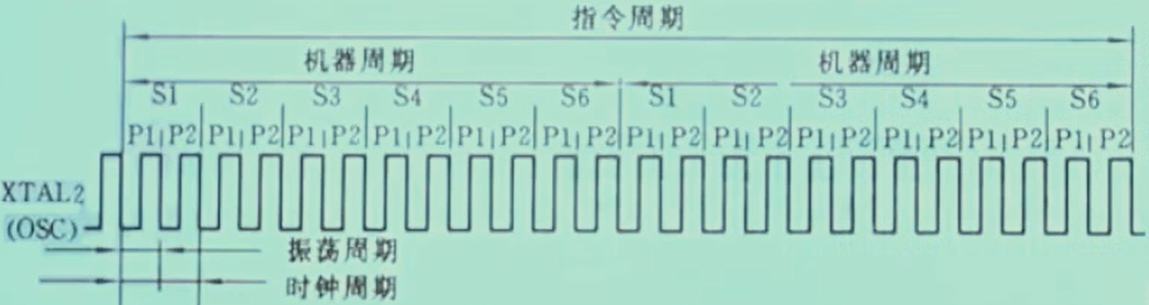

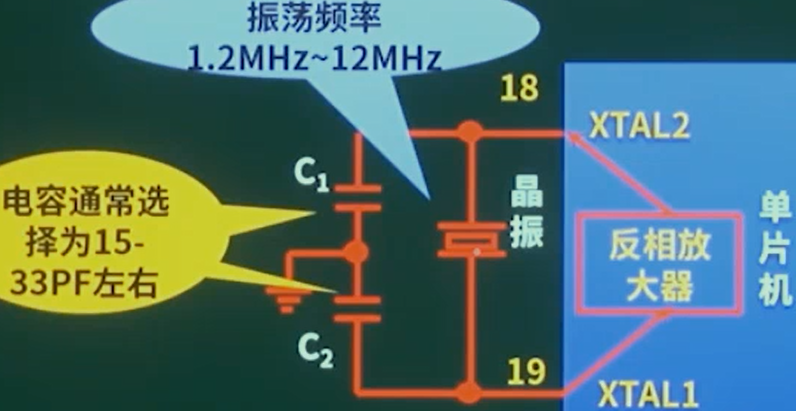

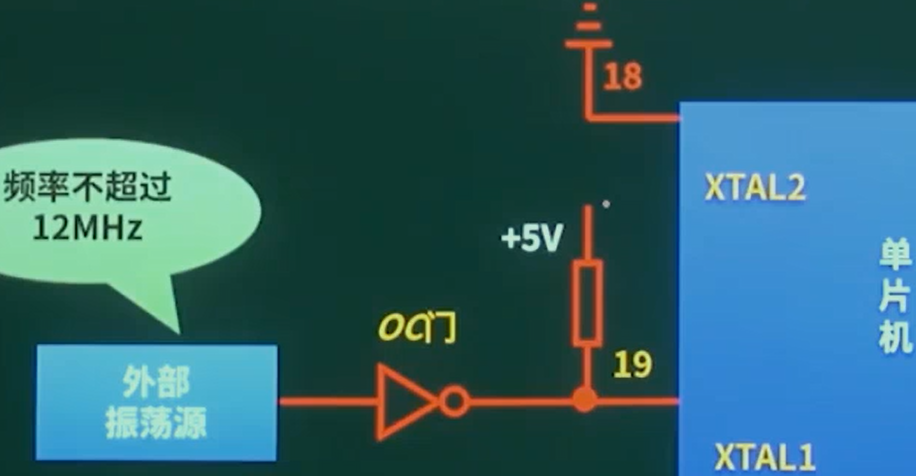

MCS-51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为垫片机产生时钟脉冲序列,振荡器的频率范围为1.2MHz~12MHz。

- 振荡周期:振荡一次所需时间。为单片机提供定时信号的振荡源的周期。

- 时钟周期:振荡脉冲二分频,又称为状态周期S。

- 机器周期:完成一个基本操作(如取指令、读存储器等)所需要的时间称为机器周期。机器周期由6个状态周期(12个振荡周期)组成。

- 指令周期:CPU执行一条指令所需要的时间可包含1~4个机器周期。

时钟电路方式。

- 内时钟方式:在XTAL1、XTAL2上外接定时元件,使其形成自激振荡器。定时元件采用由石英晶体和电容组成并联谐振电路。

- 外部时钟方式:XTAL2接地,XTAL1接外部振荡器。

4 中断系统

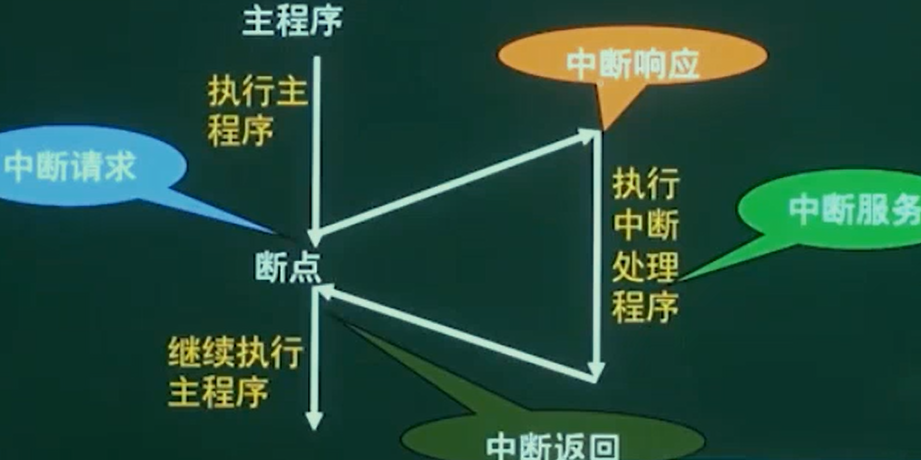

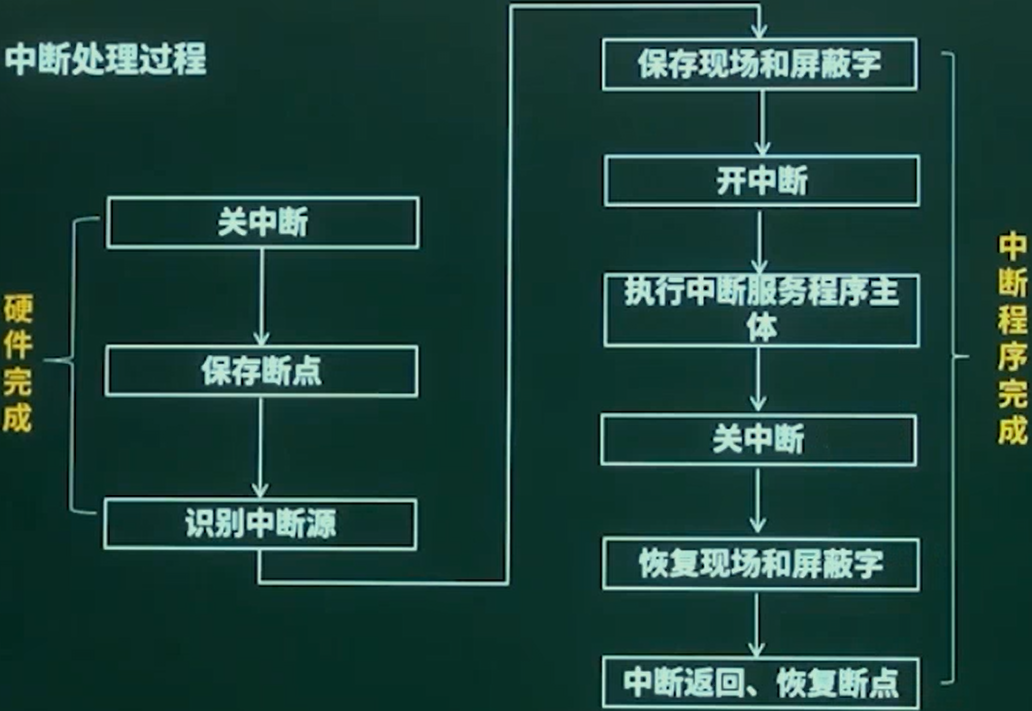

中断:CPU执行程序过程,随机接收到外设发来的中断请求,CPU可暂时中断当前正在执行的程序,转到相应的中断服务(子)程序进行处理(中断响应和中断服务)。处理完毕,再返回到原来的程序(被中断之处,即断点)(中断返回),继续运行下去,这个过程称作中断。

4.1 中断分类

请求CPU中断的设备或事件称为中断源,根据中断源的不同类别,可以把中断分为中断和内中断。

外中断:是指来自处理机和内存外部的中断,包括I/O设备发出的I/O中断、外部信号中断、各种定时器引起的时钟中断,以及程序调试中设置的断电等引起的调试中断等。外中断在狭义上一般被称为中断。

内中断:主要是指在处理机和内存内部产生的中断。内中断一般称为陷入或异常,包括程序运算引起的各种错误,如算术操作溢出、数据格式非法、除数为零等。

4.2 中断系统

中断识别:cpu响应中断后,只知道有中断请求但不知道是哪一个中断源,寻找中断源的操作过程称为中断识别。

中断识别的目的:形成该服务程序的入口地址。

| CPU识别中断的方法 | 说明 |

|---|---|

| 中断信号线法 | 每个中断源都有独立的中断请求信号线 |

| 中断软件查询法 | 中断服务程序轮询每个中断源 |

| 菊花链法 | 共享一根共同的中断请求线,中断确认信号以链式在各个模块间相连 |

| 总线仲裁法 | I/O设备在发中断请求前,先获得总线控制权,由总线仲裁机制来裁定谁可以发出中断请求信号 |

| 中断向量表法 | 根据中断号查找中断向量表来取得中断服务程序的入口地址 |

4.3 例题

- 计算机处理外部中断时,应该由操作系统保存的是(B)。

A. 程序计数器的内容

B. 通用寄存器的内容

C. 块表(TLB)的内容

D. Cache中的内容

5 16位处理器

16为微处理器:内部总线宽度为16位的微处理器。

- 比8位微处理器有较大的提高,数据宽度增加已被,实时处理能力更强,主频更高,集成度、RAM、ROM有较大的增加,更多的中断源,多路A/D转换通道等。

- MCS-96/196系列、MSP430系列、68H12系列。

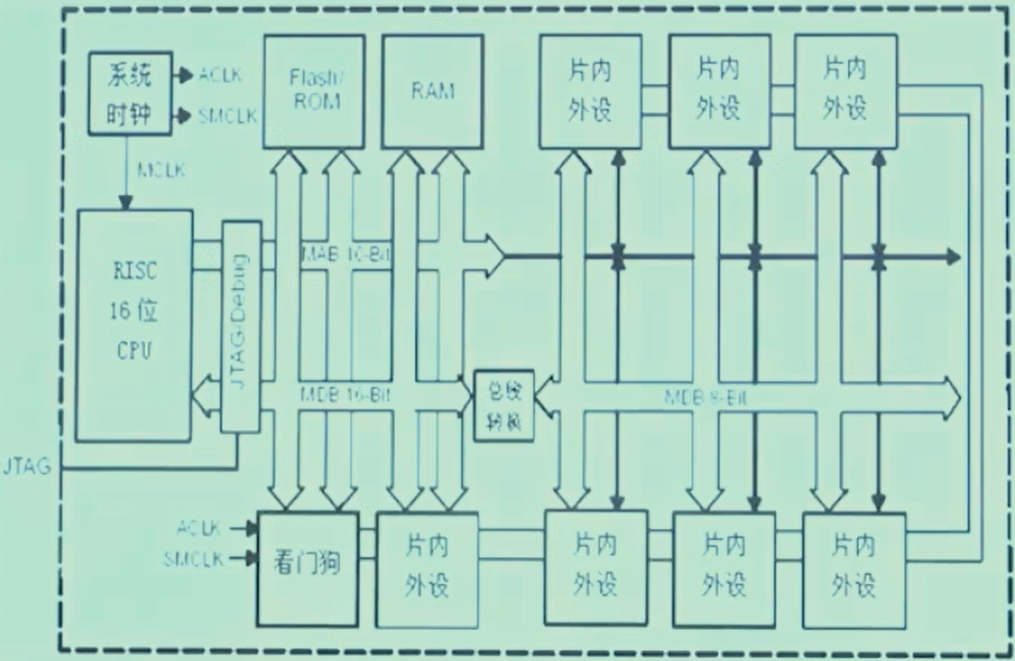

MSP430系列单片机特点。

- 超低功耗

- 16位RISC CPU,冯诺依曼架构

- 高性能模拟技术以及丰富的片上外围模块

- 系统工作稳定

- 方便高效的开发环境

- 强大的处理能力

6 JTAG

JTAG的接口是一种特殊的4/5个管脚。

- TDI(测试数据输入)

- TDO(测试数据输出)

- TCK(测试时钟)

- TMS(测试模拟选择)

- TRST(测试复位)可选。

JTAG主要应用于:电路的边界扫描测试和编程芯片的在线系统编程、调试。

- 含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如Flash,RAM,Timers等。

6.1 例题

- JTAG是用来进行嵌入式处理器调试的标准化接口,下列描述中,正确的是(A)。

A. JTAG接口上一般包括模式选择、时钟、数据输入、数据输出、复位等信号

B. 当JTAG接口上面的时钟不正常时,也可以访问CPU内部的寄存器

C. JTAG只能用于调试,而不能用于进行芯片问题的检测

D. JTAG能够访问CPU内部的寄存器,而不能访问CPU总线上面的设备

7 32位处理器

32位微处理器:采用32位地址和数据总线。其地址空间达到了4G。

&emps;主流的32位嵌入式微处理器系列。

- ARM

- MIPS

- POWER PC

- X86

- SH系列

7.1 ARM处理器

ARM处理器。

- RISC体系结构

- 每条数据处理指令当中,都控制算术逻辑单元ALU和移位器

- 自动递增和自动寻址模式

- Load-Store体系结构。指令只能把内部寄存器和立即数作为操作数,只有加载/存储(Load-Store)指令才可以访问内存

- 所有指令都可以条件执行

ARM的数据类型。

- 字节(Byte):8bits

- 半字(Half-word):16bits(2Byte)

- 字(Word):32bits(4Byte)

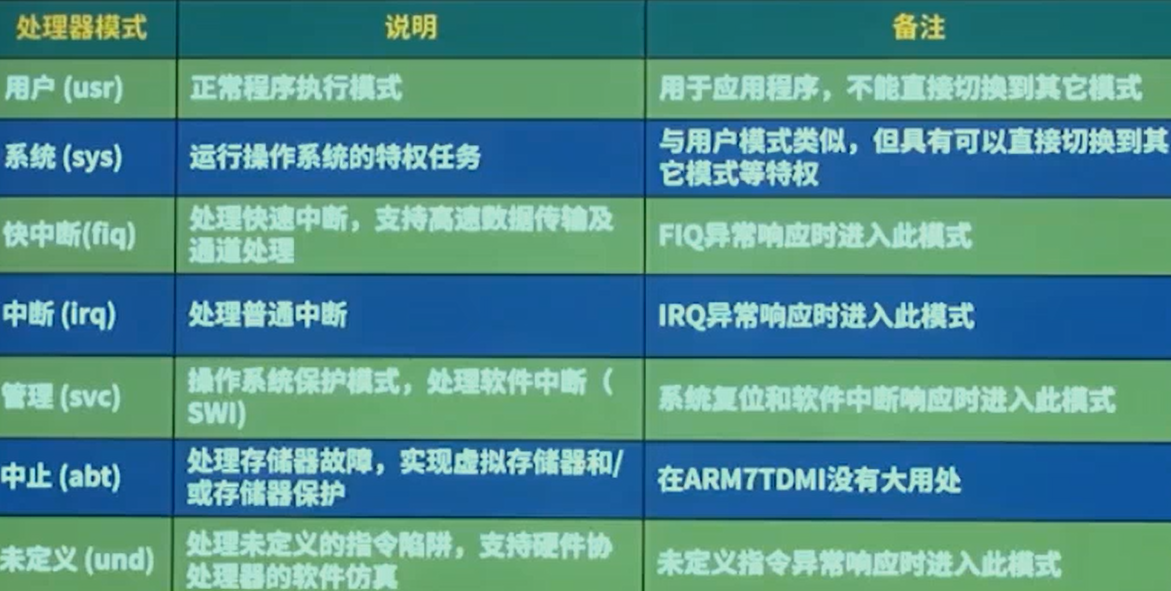

ARM处理器有7中工作模式。

7.2 存储格式

7.2.1 大端格式

大端格式下的数据存放方式。

- 字数据的高字节存储在低地址。

- 字数据的低字节存放在高地址。

7.2.2 小端格式

小端格式下的数据存放方式。

- 字数据的低字节存储在高地址。

- 字数据的高字节存放在低地址。

7.3 I/O端口的编址方法

I/O端口的编址方法:I/O端口的地址安排方式。

- 存储器映射编址

- I/O映射编址

存储器映射编址方式和I/O映射编址方式比较。

| 存储器映射编址 | I/O映射方式 | |

|---|---|---|

| 优点 | 可采用丰富的内存操作指令访问I/O单元 无需单独的I/O地址译码电路 无需专用的I/O指令 |

|

| 缺点 | 外设占用内存空间 I/O程序不易读 |

I/O操作指令仅有单一的传送指令 I/O接口需有地址译码电路 |

| 举例 | ARM中,powerpc处理器,I/O端口与内存单元统一编址 | Intel 80X86系列 I/O端口与内存单元分开编址 I/O端口有自己独立的地址空间,其大小为64kB |

7.4 例题

- 在PowerPC处理器中,内存地址与I/O地址统一编址,访问内存单元和I/O设备是靠(B)来区分的。

A. 数据总线上输出的数据

B. 不同的地址

C. 内存与I/O设备使用不同的地址总线

D. 不同的指令

8 DSP处理器

8.1 简介

DSP:Digital Signal Processing,数字信号处理。

DSP处理器:专为数字信号处理而设计的处理器,快速实现各种数字信号处理算法。

- 多总线结构,允许CPU同时进行指令和数据的访问。因而,可实现流水线操作。

- 哈佛体系结构,程序和数据空间分开,可以同时访问指令和数据。

- 数字信号处理的运算特点:乘/加,及反复相乘求和(乘积累加)

- DSP设置了硬件乘法/累加器,能在单个指令周期内完成乘法/加法运算。

DSP主要应用:信号处理、图像处理、仪器、语音处理、控制、军事、通讯、医疗、家用电器等领域。

8.2 例题

- 以下针对嵌入式DSP处理器的描述,正确的是(A)

A. 一般采用哈佛结构

B. 单片机是嵌入式DSP处理器

C. 直接在片内固化嵌入式操作系统的代码模块

D. 使用VHDL语言进行内部程序设计

8.3 体系结构特点

双核处理器:基于单个半导体的一个处理器上拥有2个处理器核心。

- 由于将2个或多个运算核封装在一个芯片上,节省了大量晶体管、封装成本

- 显著提高处理器性能

- 兼容性好

- 系统升级方便

软件角度:2个或多个内核工作协调实现方式(多核处理器运行模式):

- 对称多处理技术(SMP):将2颗完全一样的处理器封装在一个芯片内,达到双倍或接近双倍的处理性能。节省运算资源。如Power 4。

- 非对称多处理技术(AMP):2个处理内核彼此不同,各自处理和执行特定的功能,在软件的协调下分担不同的计算任务。如OMAP5910。

8.4 体系结构特点

硬件角度:按计算内核的对等与否,多核处理器可分为同构多核和异构多核。

- 同构多核:计算内核相同,地位对等的称为同构多核。

- 异构多核:计算内核不相同,地位不对等的称为异构多核。多采用“主处理核+协处理器”的设计思路。

同构多核处理器。

- Intel酷睿架构处理器

- TI keystong架构。如TMS320C6678(简称C6678)是基于KeyStone架构的高性能多核DSP。

异构多核处理器。

- AMD核显

- TI OMAP/Davinci处理器系列,典型的包括OMAP3530、Davinci DM64xx系列等。

- Xilinx Zynq处理器,如Zynq-7000全可编程SoC系列。

8.5 例题

- 以下关于多核处理器的说法中,不正确的是(B)。

A. 采用多核处理器可以降低计算机系统的功耗和体积

B. SMP、BMP和MP是多核处理器系统通常采用的三种结构,采用哪种结构与应用场景相关,而无须考虑硬件的组成差异

C. 在多核处理器中,计算机可以同时执行多个进程,而操作系统中的多个线程也可以进行并行执行

D. 多核处理器是将两个或更多的独立处理器封装在一起,集成在一个电路中

- Flynn分类法根据计算机在执行程序的过程中(A)的不同组合,将计算机分为4类。当前主流的多核计算机属于(D)计算机。

(1)

A. 指令流和数据流

B. 数据流和控制流

C. 指令流和控制流

D. 数据流和总线带宽

(2)

A. SISD

B. SIMD

C. MISD

D. MIMD

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;

2.5 Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能 至少是不实际 |

目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

2.6 例题

- Flynn分类基于信息流特征将计算机分成4类,其中()只有理论意义而无实例(B)。

A. SISD

B. MISD

C. SIMD

D. MIMI

2.7 CISC与RISC

- 复杂指令集计算机(CISC)

- 精简指令集计算机(RISC)

- 尽管RISC体系与CISC体系相比较有较多的优点,但RISC和CISC各有优势。如超长指令集。

| 序号 | 类别 | CISC | RISC |

| 1 | 指令系统 | 指令数量很多 | 较少,通常少于100 |

| 2 | 执行时间 | 有些指令执行时间很长 | 没有较长执行时间的指令 |

| 3 | 编码长度 | 编码长度可变 | 编码长度固定 |

| 4 | 寻址方式 | 寻址方式多样 | 简单寻址 |

| 5 | 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器进行算术和逻辑操作 |

| 6 | 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术 |

- 超流水线

- 超标量

- 超长指令字

2.7.1 例题

- 嵌入式处理器指令系统一般采用精简指令集(RISC)或者复杂指令集(CISC),下列关于RISC和CISC描述错误的是(C)。

A. CISC的指令种类要多于RISC

B. RISC的寻址方式复杂,CISC的寻址方式简单

C. CISC的有些指令执行时间长,RISC多为单周期指令

D. RISC中的Load/Store指令对存储器进行操作

2.8 常用嵌入式微处理器介绍

- 8位微处理器

- 16位微处理器

- 32位微处理器

- 多核处理器

3 8位处理器

8位微处理器:是指使用8位数据总线的微处理器

- 8位处理器是指使用8位数据总线的微处理器,大部分8位微处理器有16位的地址总线。

- CISC,哈佛架构。

- 具有低成本、可靠性高、可扩充内存及接口设备等特点。

- 但功能、性能和片上资源相对16位/32位/64位嵌入式微控制器来讲也较简单。

常见型号包括

- Intel的MCS-51系列

- Fairchild及Mostek公司的3870系列

3.1 MCS-51

- I/O口线:P0、P1、P2、P3

- 控制口线: $\overline{\text{PSEN}}$ 、ALE、 $\overline{\text{EA}}$ /VPP、RESET

- 电源:Vcc(+5v)、GND

- 时钟:XTAL1(片内震荡电路输入端)、XTAL2(片内振荡电路输出端)

3.2 引脚说明

3.3 时钟电路

MCS-51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为垫片机产生时钟脉冲序列,振荡器的频率范围为1.2MHz~12MHz。

- 振荡周期:振荡一次所需时间。为单片机提供定时信号的振荡源的周期。

- 时钟周期:振荡脉冲二分频,又称为状态周期S。

- 机器周期:完成一个基本操作(如取指令、读存储器等)所需要的时间称为机器周期。机器周期由6个状态周期(12个振荡周期)组成。

- 指令周期:CPU执行一条指令所需要的时间可包含1~4个机器周期。

时钟电路方式。

- 内时钟方式:在XTAL1、XTAL2上外接定时元件,使其形成自激振荡器。定时元件采用由石英晶体和电容组成并联谐振电路。

- 外部时钟方式:XTAL2接地,XTAL1接外部振荡器。

4 中断系统

中断:CPU执行程序过程,随机接收到外设发来的中断请求,CPU可暂时中断当前正在执行的程序,转到相应的中断服务(子)程序进行处理(中断响应和中断服务)。处理完毕,再返回到原来的程序(被中断之处,即断点)(中断返回),继续运行下去,这个过程称作中断。

4.1 中断分类

请求CPU中断的设备或事件称为中断源,根据中断源的不同类别,可以把中断分为中断和内中断。

外中断:是指来自处理机和内存外部的中断,包括I/O设备发出的I/O中断、外部信号中断、各种定时器引起的时钟中断,以及程序调试中设置的断电等引起的调试中断等。外中断在狭义上一般被称为中断。

内中断:主要是指在处理机和内存内部产生的中断。内中断一般称为陷入或异常,包括程序运算引起的各种错误,如算术操作溢出、数据格式非法、除数为零等。

4.2 中断系统

中断识别:cpu响应中断后,只知道有中断请求但不知道是哪一个中断源,寻找中断源的操作过程称为中断识别。

中断识别的目的:形成该服务程序的入口地址。

| CPU识别中断的方法 | 说明 |

|---|---|

| 中断信号线法 | 每个中断源都有独立的中断请求信号线 |

| 中断软件查询法 | 中断服务程序轮询每个中断源 |

| 菊花链法 | 共享一根共同的中断请求线,中断确认信号以链式在各个模块间相连 |

| 总线仲裁法 | I/O设备在发中断请求前,先获得总线控制权,由总线仲裁机制来裁定谁可以发出中断请求信号 |

| 中断向量表法 | 根据中断号查找中断向量表来取得中断服务程序的入口地址 |

4.3 例题

- 计算机处理外部中断时,应该由操作系统保存的是(B)。

A. 程序计数器的内容

B. 通用寄存器的内容

C. 块表(TLB)的内容

D. Cache中的内容

5 16位处理器

16为微处理器:内部总线宽度为16位的微处理器。

- 比8位微处理器有较大的提高,数据宽度增加已被,实时处理能力更强,主频更高,集成度、RAM、ROM有较大的增加,更多的中断源,多路A/D转换通道等。

- MCS-96/196系列、MSP430系列、68H12系列。

MSP430系列单片机特点。

- 超低功耗

- 16位RISC CPU,冯诺依曼架构

- 高性能模拟技术以及丰富的片上外围模块

- 系统工作稳定

- 方便高效的开发环境

- 强大的处理能力

6 JTAG

JTAG的接口是一种特殊的4/5个管脚。

- TDI(测试数据输入)

- TDO(测试数据输出)

- TCK(测试时钟)

- TMS(测试模拟选择)

- TRST(测试复位)可选。

JTAG主要应用于:电路的边界扫描测试和编程芯片的在线系统编程、调试。

- 含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如Flash,RAM,Timers等。

6.1 例题

- JTAG是用来进行嵌入式处理器调试的标准化接口,下列描述中,正确的是(A)。

A. JTAG接口上一般包括模式选择、时钟、数据输入、数据输出、复位等信号

B. 当JTAG接口上面的时钟不正常时,也可以访问CPU内部的寄存器

C. JTAG只能用于调试,而不能用于进行芯片问题的检测

D. JTAG能够访问CPU内部的寄存器,而不能访问CPU总线上面的设备

7 32位处理器

32位微处理器:采用32位地址和数据总线。其地址空间达到了4G。

&emps;主流的32位嵌入式微处理器系列。

- ARM

- MIPS

- POWER PC

- X86

- SH系列

7.1 ARM处理器

ARM处理器。

- RISC体系结构

- 每条数据处理指令当中,都控制算术逻辑单元ALU和移位器

- 自动递增和自动寻址模式

- Load-Store体系结构。指令只能把内部寄存器和立即数作为操作数,只有加载/存储(Load-Store)指令才可以访问内存

- 所有指令都可以条件执行

ARM的数据类型。

- 字节(Byte):8bits

- 半字(Half-word):16bits(2Byte)

- 字(Word):32bits(4Byte)

ARM处理器有7中工作模式。

7.2 存储格式

7.2.1 大端格式

大端格式下的数据存放方式。

- 字数据的高字节存储在低地址。

- 字数据的低字节存放在高地址。

7.2.2 小端格式

小端格式下的数据存放方式。

- 字数据的低字节存储在高地址。

- 字数据的高字节存放在低地址。

7.3 I/O端口的编址方法

I/O端口的编址方法:I/O端口的地址安排方式。

- 存储器映射编址

- I/O映射编址

存储器映射编址方式和I/O映射编址方式比较。

| 存储器映射编址 | I/O映射方式 | |

|---|---|---|

| 优点 | 可采用丰富的内存操作指令访问I/O单元 无需单独的I/O地址译码电路 无需专用的I/O指令 |

|

| 缺点 | 外设占用内存空间 I/O程序不易读 |

I/O操作指令仅有单一的传送指令 I/O接口需有地址译码电路 |

| 举例 | ARM中,powerpc处理器,I/O端口与内存单元统一编址 | Intel 80X86系列 I/O端口与内存单元分开编址 I/O端口有自己独立的地址空间,其大小为64kB |

7.4 例题

- 在PowerPC处理器中,内存地址与I/O地址统一编址,访问内存单元和I/O设备是靠(B)来区分的。

A. 数据总线上输出的数据

B. 不同的地址

C. 内存与I/O设备使用不同的地址总线

D. 不同的指令

8 DSP处理器

8.1 简介

DSP:Digital Signal Processing,数字信号处理。

DSP处理器:专为数字信号处理而设计的处理器,快速实现各种数字信号处理算法。

- 多总线结构,允许CPU同时进行指令和数据的访问。因而,可实现流水线操作。

- 哈佛体系结构,程序和数据空间分开,可以同时访问指令和数据。

- 数字信号处理的运算特点:乘/加,及反复相乘求和(乘积累加)

- DSP设置了硬件乘法/累加器,能在单个指令周期内完成乘法/加法运算。

DSP主要应用:信号处理、图像处理、仪器、语音处理、控制、军事、通讯、医疗、家用电器等领域。

8.2 例题

- 以下针对嵌入式DSP处理器的描述,正确的是(A)

A. 一般采用哈佛结构

B. 单片机是嵌入式DSP处理器

C. 直接在片内固化嵌入式操作系统的代码模块

D. 使用VHDL语言进行内部程序设计

8.3 体系结构特点

双核处理器:基于单个半导体的一个处理器上拥有2个处理器核心。

- 由于将2个或多个运算核封装在一个芯片上,节省了大量晶体管、封装成本

- 显著提高处理器性能

- 兼容性好

- 系统升级方便

软件角度:2个或多个内核工作协调实现方式(多核处理器运行模式):

- 对称多处理技术(SMP):将2颗完全一样的处理器封装在一个芯片内,达到双倍或接近双倍的处理性能。节省运算资源。如Power 4。

- 非对称多处理技术(AMP):2个处理内核彼此不同,各自处理和执行特定的功能,在软件的协调下分担不同的计算任务。如OMAP5910。

8.4 体系结构特点

硬件角度:按计算内核的对等与否,多核处理器可分为同构多核和异构多核。

- 同构多核:计算内核相同,地位对等的称为同构多核。

- 异构多核:计算内核不相同,地位不对等的称为异构多核。多采用“主处理核+协处理器”的设计思路。

同构多核处理器。

- Intel酷睿架构处理器

- TI keystong架构。如TMS320C6678(简称C6678)是基于KeyStone架构的高性能多核DSP。

异构多核处理器。

- AMD核显

- TI OMAP/Davinci处理器系列,典型的包括OMAP3530、Davinci DM64xx系列等。

- Xilinx Zynq处理器,如Zynq-7000全可编程SoC系列。

8.5 例题

- 以下关于多核处理器的说法中,不正确的是(B)。

A. 采用多核处理器可以降低计算机系统的功耗和体积

B. SMP、BMP和MP是多核处理器系统通常采用的三种结构,采用哪种结构与应用场景相关,而无须考虑硬件的组成差异

C. 在多核处理器中,计算机可以同时执行多个进程,而操作系统中的多个线程也可以进行并行执行

D. 多核处理器是将两个或更多的独立处理器封装在一起,集成在一个电路中

- Flynn分类法根据计算机在执行程序的过程中(A)的不同组合,将计算机分为4类。当前主流的多核计算机属于(D)计算机。

(1)

A. 指令流和数据流

B. 数据流和控制流

C. 指令流和控制流

D. 数据流和总线带宽

(2)

A. SISD

B. SIMD

C. MISD

D. MIMD

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;

2.5 Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能 至少是不实际 |

目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

2.6 例题

- Flynn分类基于信息流特征将计算机分成4类,其中()只有理论意义而无实例(B)。

A. SISD

B. MISD

C. SIMD

D. MIMI

2.7 CISC与RISC

- 复杂指令集计算机(CISC)

- 精简指令集计算机(RISC)

- 尽管RISC体系与CISC体系相比较有较多的优点,但RISC和CISC各有优势。如超长指令集。

| 序号 | 类别 | CISC | RISC |

| 1 | 指令系统 | 指令数量很多 | 较少,通常少于100 |

| 2 | 执行时间 | 有些指令执行时间很长 | 没有较长执行时间的指令 |

| 3 | 编码长度 | 编码长度可变 | 编码长度固定 |

| 4 | 寻址方式 | 寻址方式多样 | 简单寻址 |

| 5 | 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器进行算术和逻辑操作 |

| 6 | 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术 |

- 超流水线

- 超标量

- 超长指令字

2.7.1 例题

- 嵌入式处理器指令系统一般采用精简指令集(RISC)或者复杂指令集(CISC),下列关于RISC和CISC描述错误的是(C)。

A. CISC的指令种类要多于RISC

B. RISC的寻址方式复杂,CISC的寻址方式简单

C. CISC的有些指令执行时间长,RISC多为单周期指令

D. RISC中的Load/Store指令对存储器进行操作

2.8 常用嵌入式微处理器介绍

- 8位微处理器

- 16位微处理器

- 32位微处理器

- 多核处理器

3 8位处理器

8位微处理器:是指使用8位数据总线的微处理器

- 8位处理器是指使用8位数据总线的微处理器,大部分8位微处理器有16位的地址总线。

- CISC,哈佛架构。

- 具有低成本、可靠性高、可扩充内存及接口设备等特点。

- 但功能、性能和片上资源相对16位/32位/64位嵌入式微控制器来讲也较简单。

常见型号包括

- Intel的MCS-51系列

- Fairchild及Mostek公司的3870系列

3.1 MCS-51

- I/O口线:P0、P1、P2、P3

- 控制口线: $\overline{\text{PSEN}}$ 、ALE、 $\overline{\text{EA}}$ /VPP、RESET

- 电源:Vcc(+5v)、GND

- 时钟:XTAL1(片内震荡电路输入端)、XTAL2(片内振荡电路输出端)

3.2 引脚说明

3.3 时钟电路

MCS-51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为垫片机产生时钟脉冲序列,振荡器的频率范围为1.2MHz~12MHz。

- 振荡周期:振荡一次所需时间。为单片机提供定时信号的振荡源的周期。

- 时钟周期:振荡脉冲二分频,又称为状态周期S。

- 机器周期:完成一个基本操作(如取指令、读存储器等)所需要的时间称为机器周期。机器周期由6个状态周期(12个振荡周期)组成。

- 指令周期:CPU执行一条指令所需要的时间可包含1~4个机器周期。

时钟电路方式。

- 内时钟方式:在XTAL1、XTAL2上外接定时元件,使其形成自激振荡器。定时元件采用由石英晶体和电容组成并联谐振电路。

- 外部时钟方式:XTAL2接地,XTAL1接外部振荡器。

4 中断系统

中断:CPU执行程序过程,随机接收到外设发来的中断请求,CPU可暂时中断当前正在执行的程序,转到相应的中断服务(子)程序进行处理(中断响应和中断服务)。处理完毕,再返回到原来的程序(被中断之处,即断点)(中断返回),继续运行下去,这个过程称作中断。

4.1 中断分类

请求CPU中断的设备或事件称为中断源,根据中断源的不同类别,可以把中断分为中断和内中断。

外中断:是指来自处理机和内存外部的中断,包括I/O设备发出的I/O中断、外部信号中断、各种定时器引起的时钟中断,以及程序调试中设置的断电等引起的调试中断等。外中断在狭义上一般被称为中断。

内中断:主要是指在处理机和内存内部产生的中断。内中断一般称为陷入或异常,包括程序运算引起的各种错误,如算术操作溢出、数据格式非法、除数为零等。

4.2 中断系统

中断识别:cpu响应中断后,只知道有中断请求但不知道是哪一个中断源,寻找中断源的操作过程称为中断识别。

中断识别的目的:形成该服务程序的入口地址。

| CPU识别中断的方法 | 说明 |

|---|---|

| 中断信号线法 | 每个中断源都有独立的中断请求信号线 |

| 中断软件查询法 | 中断服务程序轮询每个中断源 |

| 菊花链法 | 共享一根共同的中断请求线,中断确认信号以链式在各个模块间相连 |

| 总线仲裁法 | I/O设备在发中断请求前,先获得总线控制权,由总线仲裁机制来裁定谁可以发出中断请求信号 |

| 中断向量表法 | 根据中断号查找中断向量表来取得中断服务程序的入口地址 |

4.3 例题

- 计算机处理外部中断时,应该由操作系统保存的是(B)。

A. 程序计数器的内容

B. 通用寄存器的内容

C. 块表(TLB)的内容

D. Cache中的内容

5 16位处理器

16为微处理器:内部总线宽度为16位的微处理器。

- 比8位微处理器有较大的提高,数据宽度增加已被,实时处理能力更强,主频更高,集成度、RAM、ROM有较大的增加,更多的中断源,多路A/D转换通道等。

- MCS-96/196系列、MSP430系列、68H12系列。

MSP430系列单片机特点。

- 超低功耗

- 16位RISC CPU,冯诺依曼架构

- 高性能模拟技术以及丰富的片上外围模块

- 系统工作稳定

- 方便高效的开发环境

- 强大的处理能力

6 JTAG

JTAG的接口是一种特殊的4/5个管脚。

- TDI(测试数据输入)

- TDO(测试数据输出)

- TCK(测试时钟)

- TMS(测试模拟选择)

- TRST(测试复位)可选。

JTAG主要应用于:电路的边界扫描测试和编程芯片的在线系统编程、调试。

- 含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如Flash,RAM,Timers等。

6.1 例题

- JTAG是用来进行嵌入式处理器调试的标准化接口,下列描述中,正确的是(A)。

A. JTAG接口上一般包括模式选择、时钟、数据输入、数据输出、复位等信号

B. 当JTAG接口上面的时钟不正常时,也可以访问CPU内部的寄存器

C. JTAG只能用于调试,而不能用于进行芯片问题的检测

D. JTAG能够访问CPU内部的寄存器,而不能访问CPU总线上面的设备

7 32位处理器

32位微处理器:采用32位地址和数据总线。其地址空间达到了4G。

&emps;主流的32位嵌入式微处理器系列。

- ARM

- MIPS

- POWER PC

- X86

- SH系列

7.1 ARM处理器

ARM处理器。

- RISC体系结构

- 每条数据处理指令当中,都控制算术逻辑单元ALU和移位器

- 自动递增和自动寻址模式

- Load-Store体系结构。指令只能把内部寄存器和立即数作为操作数,只有加载/存储(Load-Store)指令才可以访问内存

- 所有指令都可以条件执行

ARM的数据类型。

- 字节(Byte):8bits

- 半字(Half-word):16bits(2Byte)

- 字(Word):32bits(4Byte)

ARM处理器有7中工作模式。

7.2 存储格式

7.2.1 大端格式

大端格式下的数据存放方式。

- 字数据的高字节存储在低地址。

- 字数据的低字节存放在高地址。

7.2.2 小端格式

小端格式下的数据存放方式。

- 字数据的低字节存储在高地址。

- 字数据的高字节存放在低地址。

7.3 I/O端口的编址方法

I/O端口的编址方法:I/O端口的地址安排方式。

- 存储器映射编址

- I/O映射编址

存储器映射编址方式和I/O映射编址方式比较。

| 存储器映射编址 | I/O映射方式 | |

|---|---|---|

| 优点 | 可采用丰富的内存操作指令访问I/O单元 无需单独的I/O地址译码电路 无需专用的I/O指令 |

|

| 缺点 | 外设占用内存空间 I/O程序不易读 |

I/O操作指令仅有单一的传送指令 I/O接口需有地址译码电路 |

| 举例 | ARM中,powerpc处理器,I/O端口与内存单元统一编址 | Intel 80X86系列 I/O端口与内存单元分开编址 I/O端口有自己独立的地址空间,其大小为64kB |

7.4 例题

- 在PowerPC处理器中,内存地址与I/O地址统一编址,访问内存单元和I/O设备是靠(B)来区分的。

A. 数据总线上输出的数据

B. 不同的地址

C. 内存与I/O设备使用不同的地址总线

D. 不同的指令

8 DSP处理器

8.1 简介

DSP:Digital Signal Processing,数字信号处理。

DSP处理器:专为数字信号处理而设计的处理器,快速实现各种数字信号处理算法。

- 多总线结构,允许CPU同时进行指令和数据的访问。因而,可实现流水线操作。

- 哈佛体系结构,程序和数据空间分开,可以同时访问指令和数据。

- 数字信号处理的运算特点:乘/加,及反复相乘求和(乘积累加)

- DSP设置了硬件乘法/累加器,能在单个指令周期内完成乘法/加法运算。

DSP主要应用:信号处理、图像处理、仪器、语音处理、控制、军事、通讯、医疗、家用电器等领域。

8.2 例题

- 以下针对嵌入式DSP处理器的描述,正确的是(A)

A. 一般采用哈佛结构

B. 单片机是嵌入式DSP处理器

C. 直接在片内固化嵌入式操作系统的代码模块

D. 使用VHDL语言进行内部程序设计

8.3 体系结构特点

双核处理器:基于单个半导体的一个处理器上拥有2个处理器核心。

- 由于将2个或多个运算核封装在一个芯片上,节省了大量晶体管、封装成本

- 显著提高处理器性能

- 兼容性好

- 系统升级方便

软件角度:2个或多个内核工作协调实现方式(多核处理器运行模式):

- 对称多处理技术(SMP):将2颗完全一样的处理器封装在一个芯片内,达到双倍或接近双倍的处理性能。节省运算资源。如Power 4。

- 非对称多处理技术(AMP):2个处理内核彼此不同,各自处理和执行特定的功能,在软件的协调下分担不同的计算任务。如OMAP5910。

8.4 体系结构特点

硬件角度:按计算内核的对等与否,多核处理器可分为同构多核和异构多核。

- 同构多核:计算内核相同,地位对等的称为同构多核。

- 异构多核:计算内核不相同,地位不对等的称为异构多核。多采用“主处理核+协处理器”的设计思路。

同构多核处理器。

- Intel酷睿架构处理器

- TI keystong架构。如TMS320C6678(简称C6678)是基于KeyStone架构的高性能多核DSP。

异构多核处理器。

- AMD核显

- TI OMAP/Davinci处理器系列,典型的包括OMAP3530、Davinci DM64xx系列等。

- Xilinx Zynq处理器,如Zynq-7000全可编程SoC系列。

8.5 例题

- 以下关于多核处理器的说法中,不正确的是(B)。

A. 采用多核处理器可以降低计算机系统的功耗和体积

B. SMP、BMP和MP是多核处理器系统通常采用的三种结构,采用哪种结构与应用场景相关,而无须考虑硬件的组成差异

C. 在多核处理器中,计算机可以同时执行多个进程,而操作系统中的多个线程也可以进行并行执行

D. 多核处理器是将两个或更多的独立处理器封装在一起,集成在一个电路中

- Flynn分类法根据计算机在执行程序的过程中(A)的不同组合,将计算机分为4类。当前主流的多核计算机属于(D)计算机。

(1)

A. 指令流和数据流

B. 数据流和控制流

C. 指令流和控制流

D. 数据流和总线带宽

(2)

A. SISD

B. SIMD

C. MISD

D. MIMD

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;

2.5 Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能 至少是不实际 |

目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

2.6 例题

- Flynn分类基于信息流特征将计算机分成4类,其中()只有理论意义而无实例(B)。

A. SISD

B. MISD

C. SIMD

D. MIMI

2.7 CISC与RISC

- 复杂指令集计算机(CISC)

- 精简指令集计算机(RISC)

- 尽管RISC体系与CISC体系相比较有较多的优点,但RISC和CISC各有优势。如超长指令集。

| 序号 | 类别 | CISC | RISC |

| 1 | 指令系统 | 指令数量很多 | 较少,通常少于100 |

| 2 | 执行时间 | 有些指令执行时间很长 | 没有较长执行时间的指令 |

| 3 | 编码长度 | 编码长度可变 | 编码长度固定 |

| 4 | 寻址方式 | 寻址方式多样 | 简单寻址 |

| 5 | 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器进行算术和逻辑操作 |

| 6 | 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术 |

- 超流水线

- 超标量

- 超长指令字

2.7.1 例题

- 嵌入式处理器指令系统一般采用精简指令集(RISC)或者复杂指令集(CISC),下列关于RISC和CISC描述错误的是(C)。

A. CISC的指令种类要多于RISC

B. RISC的寻址方式复杂,CISC的寻址方式简单

C. CISC的有些指令执行时间长,RISC多为单周期指令

D. RISC中的Load/Store指令对存储器进行操作

2.8 常用嵌入式微处理器介绍

- 8位微处理器

- 16位微处理器

- 32位微处理器

- 多核处理器

3 8位处理器

8位微处理器:是指使用8位数据总线的微处理器

- 8位处理器是指使用8位数据总线的微处理器,大部分8位微处理器有16位的地址总线。

- CISC,哈佛架构。

- 具有低成本、可靠性高、可扩充内存及接口设备等特点。

- 但功能、性能和片上资源相对16位/32位/64位嵌入式微控制器来讲也较简单。

常见型号包括

- Intel的MCS-51系列

- Fairchild及Mostek公司的3870系列

3.1 MCS-51

- I/O口线:P0、P1、P2、P3

- 控制口线: $\overline{\text{PSEN}}$ 、ALE、 $\overline{\text{EA}}$ /VPP、RESET

- 电源:Vcc(+5v)、GND

- 时钟:XTAL1(片内震荡电路输入端)、XTAL2(片内振荡电路输出端)

3.2 引脚说明

3.3 时钟电路

MCS-51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为垫片机产生时钟脉冲序列,振荡器的频率范围为1.2MHz~12MHz。

- 振荡周期:振荡一次所需时间。为单片机提供定时信号的振荡源的周期。

- 时钟周期:振荡脉冲二分频,又称为状态周期S。

- 机器周期:完成一个基本操作(如取指令、读存储器等)所需要的时间称为机器周期。机器周期由6个状态周期(12个振荡周期)组成。

- 指令周期:CPU执行一条指令所需要的时间可包含1~4个机器周期。

时钟电路方式。

- 内时钟方式:在XTAL1、XTAL2上外接定时元件,使其形成自激振荡器。定时元件采用由石英晶体和电容组成并联谐振电路。

- 外部时钟方式:XTAL2接地,XTAL1接外部振荡器。

4 中断系统

中断:CPU执行程序过程,随机接收到外设发来的中断请求,CPU可暂时中断当前正在执行的程序,转到相应的中断服务(子)程序进行处理(中断响应和中断服务)。处理完毕,再返回到原来的程序(被中断之处,即断点)(中断返回),继续运行下去,这个过程称作中断。

4.1 中断分类

请求CPU中断的设备或事件称为中断源,根据中断源的不同类别,可以把中断分为中断和内中断。

外中断:是指来自处理机和内存外部的中断,包括I/O设备发出的I/O中断、外部信号中断、各种定时器引起的时钟中断,以及程序调试中设置的断电等引起的调试中断等。外中断在狭义上一般被称为中断。

内中断:主要是指在处理机和内存内部产生的中断。内中断一般称为陷入或异常,包括程序运算引起的各种错误,如算术操作溢出、数据格式非法、除数为零等。

4.2 中断系统

中断识别:cpu响应中断后,只知道有中断请求但不知道是哪一个中断源,寻找中断源的操作过程称为中断识别。

中断识别的目的:形成该服务程序的入口地址。

| CPU识别中断的方法 | 说明 |

|---|---|

| 中断信号线法 | 每个中断源都有独立的中断请求信号线 |

| 中断软件查询法 | 中断服务程序轮询每个中断源 |

| 菊花链法 | 共享一根共同的中断请求线,中断确认信号以链式在各个模块间相连 |

| 总线仲裁法 | I/O设备在发中断请求前,先获得总线控制权,由总线仲裁机制来裁定谁可以发出中断请求信号 |

| 中断向量表法 | 根据中断号查找中断向量表来取得中断服务程序的入口地址 |

4.3 例题

- 计算机处理外部中断时,应该由操作系统保存的是(B)。

A. 程序计数器的内容

B. 通用寄存器的内容

C. 块表(TLB)的内容

D. Cache中的内容

5 16位处理器

16为微处理器:内部总线宽度为16位的微处理器。

- 比8位微处理器有较大的提高,数据宽度增加已被,实时处理能力更强,主频更高,集成度、RAM、ROM有较大的增加,更多的中断源,多路A/D转换通道等。

- MCS-96/196系列、MSP430系列、68H12系列。

MSP430系列单片机特点。

- 超低功耗

- 16位RISC CPU,冯诺依曼架构

- 高性能模拟技术以及丰富的片上外围模块

- 系统工作稳定

- 方便高效的开发环境

- 强大的处理能力

6 JTAG

JTAG的接口是一种特殊的4/5个管脚。

- TDI(测试数据输入)

- TDO(测试数据输出)

- TCK(测试时钟)

- TMS(测试模拟选择)

- TRST(测试复位)可选。

JTAG主要应用于:电路的边界扫描测试和编程芯片的在线系统编程、调试。

- 含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如Flash,RAM,Timers等。

6.1 例题

- JTAG是用来进行嵌入式处理器调试的标准化接口,下列描述中,正确的是(A)。

A. JTAG接口上一般包括模式选择、时钟、数据输入、数据输出、复位等信号

B. 当JTAG接口上面的时钟不正常时,也可以访问CPU内部的寄存器

C. JTAG只能用于调试,而不能用于进行芯片问题的检测

D. JTAG能够访问CPU内部的寄存器,而不能访问CPU总线上面的设备

7 32位处理器

32位微处理器:采用32位地址和数据总线。其地址空间达到了4G。

&emps;主流的32位嵌入式微处理器系列。

- ARM

- MIPS

- POWER PC

- X86

- SH系列

7.1 ARM处理器

ARM处理器。

- RISC体系结构

- 每条数据处理指令当中,都控制算术逻辑单元ALU和移位器

- 自动递增和自动寻址模式

- Load-Store体系结构。指令只能把内部寄存器和立即数作为操作数,只有加载/存储(Load-Store)指令才可以访问内存

- 所有指令都可以条件执行

ARM的数据类型。

- 字节(Byte):8bits

- 半字(Half-word):16bits(2Byte)

- 字(Word):32bits(4Byte)

ARM处理器有7中工作模式。

7.2 存储格式

7.2.1 大端格式

大端格式下的数据存放方式。

- 字数据的高字节存储在低地址。

- 字数据的低字节存放在高地址。

7.2.2 小端格式

小端格式下的数据存放方式。

- 字数据的低字节存储在高地址。

- 字数据的高字节存放在低地址。

7.3 I/O端口的编址方法

I/O端口的编址方法:I/O端口的地址安排方式。

- 存储器映射编址

- I/O映射编址

存储器映射编址方式和I/O映射编址方式比较。

| 存储器映射编址 | I/O映射方式 | |

|---|---|---|

| 优点 | 可采用丰富的内存操作指令访问I/O单元 无需单独的I/O地址译码电路 无需专用的I/O指令 |

|

| 缺点 | 外设占用内存空间 I/O程序不易读 |

I/O操作指令仅有单一的传送指令 I/O接口需有地址译码电路 |

| 举例 | ARM中,powerpc处理器,I/O端口与内存单元统一编址 | Intel 80X86系列 I/O端口与内存单元分开编址 I/O端口有自己独立的地址空间,其大小为64kB |

7.4 例题

- 在PowerPC处理器中,内存地址与I/O地址统一编址,访问内存单元和I/O设备是靠(B)来区分的。

A. 数据总线上输出的数据

B. 不同的地址

C. 内存与I/O设备使用不同的地址总线

D. 不同的指令

8 DSP处理器

8.1 简介

DSP:Digital Signal Processing,数字信号处理。

DSP处理器:专为数字信号处理而设计的处理器,快速实现各种数字信号处理算法。

- 多总线结构,允许CPU同时进行指令和数据的访问。因而,可实现流水线操作。

- 哈佛体系结构,程序和数据空间分开,可以同时访问指令和数据。

- 数字信号处理的运算特点:乘/加,及反复相乘求和(乘积累加)

- DSP设置了硬件乘法/累加器,能在单个指令周期内完成乘法/加法运算。

DSP主要应用:信号处理、图像处理、仪器、语音处理、控制、军事、通讯、医疗、家用电器等领域。

8.2 例题

- 以下针对嵌入式DSP处理器的描述,正确的是(A)

A. 一般采用哈佛结构

B. 单片机是嵌入式DSP处理器

C. 直接在片内固化嵌入式操作系统的代码模块

D. 使用VHDL语言进行内部程序设计

8.3 体系结构特点

双核处理器:基于单个半导体的一个处理器上拥有2个处理器核心。

- 由于将2个或多个运算核封装在一个芯片上,节省了大量晶体管、封装成本

- 显著提高处理器性能

- 兼容性好

- 系统升级方便

软件角度:2个或多个内核工作协调实现方式(多核处理器运行模式):

- 对称多处理技术(SMP):将2颗完全一样的处理器封装在一个芯片内,达到双倍或接近双倍的处理性能。节省运算资源。如Power 4。

- 非对称多处理技术(AMP):2个处理内核彼此不同,各自处理和执行特定的功能,在软件的协调下分担不同的计算任务。如OMAP5910。

8.4 体系结构特点

硬件角度:按计算内核的对等与否,多核处理器可分为同构多核和异构多核。

- 同构多核:计算内核相同,地位对等的称为同构多核。

- 异构多核:计算内核不相同,地位不对等的称为异构多核。多采用“主处理核+协处理器”的设计思路。

同构多核处理器。

- Intel酷睿架构处理器

- TI keystong架构。如TMS320C6678(简称C6678)是基于KeyStone架构的高性能多核DSP。

异构多核处理器。

- AMD核显

- TI OMAP/Davinci处理器系列,典型的包括OMAP3530、Davinci DM64xx系列等。

- Xilinx Zynq处理器,如Zynq-7000全可编程SoC系列。

8.5 例题

- 以下关于多核处理器的说法中,不正确的是(B)。

A. 采用多核处理器可以降低计算机系统的功耗和体积

B. SMP、BMP和MP是多核处理器系统通常采用的三种结构,采用哪种结构与应用场景相关,而无须考虑硬件的组成差异

C. 在多核处理器中,计算机可以同时执行多个进程,而操作系统中的多个线程也可以进行并行执行

D. 多核处理器是将两个或更多的独立处理器封装在一起,集成在一个电路中

- Flynn分类法根据计算机在执行程序的过程中(A)的不同组合,将计算机分为4类。当前主流的多核计算机属于(D)计算机。

(1)

A. 指令流和数据流

B. 数据流和控制流

C. 指令流和控制流

D. 数据流和总线带宽

(2)

A. SISD

B. SIMD

C. MISD

D. MIMD

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;

2.5 Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能 至少是不实际 |

目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

2.6 例题

- Flynn分类基于信息流特征将计算机分成4类,其中()只有理论意义而无实例(B)。

A. SISD

B. MISD

C. SIMD

D. MIMI

2.7 CISC与RISC

- 复杂指令集计算机(CISC)

- 精简指令集计算机(RISC)

- 尽管RISC体系与CISC体系相比较有较多的优点,但RISC和CISC各有优势。如超长指令集。

| 序号 | 类别 | CISC | RISC |

| 1 | 指令系统 | 指令数量很多 | 较少,通常少于100 |

| 2 | 执行时间 | 有些指令执行时间很长 | 没有较长执行时间的指令 |

| 3 | 编码长度 | 编码长度可变 | 编码长度固定 |

| 4 | 寻址方式 | 寻址方式多样 | 简单寻址 |

| 5 | 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器进行算术和逻辑操作 |

| 6 | 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术 |

- 超流水线

- 超标量

- 超长指令字

2.7.1 例题

- 嵌入式处理器指令系统一般采用精简指令集(RISC)或者复杂指令集(CISC),下列关于RISC和CISC描述错误的是(C)。

A. CISC的指令种类要多于RISC

B. RISC的寻址方式复杂,CISC的寻址方式简单

C. CISC的有些指令执行时间长,RISC多为单周期指令

D. RISC中的Load/Store指令对存储器进行操作

2.8 常用嵌入式微处理器介绍

- 8位微处理器

- 16位微处理器

- 32位微处理器

- 多核处理器

3 8位处理器

8位微处理器:是指使用8位数据总线的微处理器

- 8位处理器是指使用8位数据总线的微处理器,大部分8位微处理器有16位的地址总线。

- CISC,哈佛架构。

- 具有低成本、可靠性高、可扩充内存及接口设备等特点。

- 但功能、性能和片上资源相对16位/32位/64位嵌入式微控制器来讲也较简单。

常见型号包括

- Intel的MCS-51系列

- Fairchild及Mostek公司的3870系列

3.1 MCS-51

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;

2.5 Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能 至少是不实际 |

目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

2.6 例题

- Flynn分类基于信息流特征将计算机分成4类,其中()只有理论意义而无实例(B)。

A. SISD

B. MISD

C. SIMD

D. MIMI

2.7 CISC与RISC

- 复杂指令集计算机(CISC)

- 精简指令集计算机(RISC)

- 尽管RISC体系与CISC体系相比较有较多的优点,但RISC和CISC各有优势。如超长指令集。

| 序号 | 类别 | CISC | RISC |

| 1 | 指令系统 | 指令数量很多 | 较少,通常少于100 |

| 2 | 执行时间 | 有些指令执行时间很长 | 没有较长执行时间的指令 |

| 3 | 编码长度 | 编码长度可变 | 编码长度固定 |

| 4 | 寻址方式 | 寻址方式多样 | 简单寻址 |

| 5 | 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器进行算术和逻辑操作 |

| 6 | 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术 |

- 超流水线

- 超标量

- 超长指令字

2.7.1 例题

- 嵌入式处理器指令系统一般采用精简指令集(RISC)或者复杂指令集(CISC),下列关于RISC和CISC描述错误的是(C)。

A. CISC的指令种类要多于RISC

B. RISC的寻址方式复杂,CISC的寻址方式简单

C. CISC的有些指令执行时间长,RISC多为单周期指令

D. RISC中的Load/Store指令对存储器进行操作

2.8 常用嵌入式微处理器介绍

- 8位微处理器

- 16位微处理器

- 32位微处理器

- 多核处理器

3 8位处理器

8位微处理器:是指使用8位数据总线的微处理器

- 8位处理器是指使用8位数据总线的微处理器,大部分8位微处理器有16位的地址总线。

- CISC,哈佛架构。

- 具有低成本、可靠性高、可扩充内存及接口设备等特点。

- 但功能、性能和片上资源相对16位/32位/64位嵌入式微控制器来讲也较简单。

常见型号包括

- Intel的MCS-51系列

- Fairchild及Mostek公司的3870系列

3.1 MCS-51

- I/O口线:P0、P1、P2、P3

- 控制口线: $\overline{\text{PSEN}}$ 、ALE、 $\overline{\text{EA}}$ /VPP、RESET

- 电源:Vcc(+5v)、GND

- 时钟:XTAL1(片内震荡电路输入端)、XTAL2(片内振荡电路输出端)

3.2 引脚说明

3.3 时钟电路

MCS-51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为垫片机产生时钟脉冲序列,振荡器的频率范围为1.2MHz~12MHz。

- 振荡周期:振荡一次所需时间。为单片机提供定时信号的振荡源的周期。

- 时钟周期:振荡脉冲二分频,又称为状态周期S。

- 机器周期:完成一个基本操作(如取指令、读存储器等)所需要的时间称为机器周期。机器周期由6个状态周期(12个振荡周期)组成。

- 指令周期:CPU执行一条指令所需要的时间可包含1~4个机器周期。

时钟电路方式。

- 内时钟方式:在XTAL1、XTAL2上外接定时元件,使其形成自激振荡器。定时元件采用由石英晶体和电容组成并联谐振电路。

- 外部时钟方式:XTAL2接地,XTAL1接外部振荡器。

4 中断系统

中断:CPU执行程序过程,随机接收到外设发来的中断请求,CPU可暂时中断当前正在执行的程序,转到相应的中断服务(子)程序进行处理(中断响应和中断服务)。处理完毕,再返回到原来的程序(被中断之处,即断点)(中断返回),继续运行下去,这个过程称作中断。

4.1 中断分类

请求CPU中断的设备或事件称为中断源,根据中断源的不同类别,可以把中断分为中断和内中断。

外中断:是指来自处理机和内存外部的中断,包括I/O设备发出的I/O中断、外部信号中断、各种定时器引起的时钟中断,以及程序调试中设置的断电等引起的调试中断等。外中断在狭义上一般被称为中断。

内中断:主要是指在处理机和内存内部产生的中断。内中断一般称为陷入或异常,包括程序运算引起的各种错误,如算术操作溢出、数据格式非法、除数为零等。

4.2 中断系统

中断识别:cpu响应中断后,只知道有中断请求但不知道是哪一个中断源,寻找中断源的操作过程称为中断识别。

中断识别的目的:形成该服务程序的入口地址。

| CPU识别中断的方法 | 说明 |

|---|---|

| 中断信号线法 | 每个中断源都有独立的中断请求信号线 |

| 中断软件查询法 | 中断服务程序轮询每个中断源 |

| 菊花链法 | 共享一根共同的中断请求线,中断确认信号以链式在各个模块间相连 |

| 总线仲裁法 | I/O设备在发中断请求前,先获得总线控制权,由总线仲裁机制来裁定谁可以发出中断请求信号 |

| 中断向量表法 | 根据中断号查找中断向量表来取得中断服务程序的入口地址 |

4.3 例题

- 计算机处理外部中断时,应该由操作系统保存的是(B)。

A. 程序计数器的内容

B. 通用寄存器的内容

C. 块表(TLB)的内容

D. Cache中的内容

5 16位处理器

16为微处理器:内部总线宽度为16位的微处理器。

- 比8位微处理器有较大的提高,数据宽度增加已被,实时处理能力更强,主频更高,集成度、RAM、ROM有较大的增加,更多的中断源,多路A/D转换通道等。

- MCS-96/196系列、MSP430系列、68H12系列。

MSP430系列单片机特点。

- 超低功耗

- 16位RISC CPU,冯诺依曼架构

- 高性能模拟技术以及丰富的片上外围模块

- 系统工作稳定

- 方便高效的开发环境

- 强大的处理能力

6 JTAG

JTAG的接口是一种特殊的4/5个管脚。

- TDI(测试数据输入)

- TDO(测试数据输出)

- TCK(测试时钟)

- TMS(测试模拟选择)

- TRST(测试复位)可选。

JTAG主要应用于:电路的边界扫描测试和编程芯片的在线系统编程、调试。

- 含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如Flash,RAM,Timers等。

6.1 例题

- JTAG是用来进行嵌入式处理器调试的标准化接口,下列描述中,正确的是(A)。

A. JTAG接口上一般包括模式选择、时钟、数据输入、数据输出、复位等信号

B. 当JTAG接口上面的时钟不正常时,也可以访问CPU内部的寄存器

C. JTAG只能用于调试,而不能用于进行芯片问题的检测

D. JTAG能够访问CPU内部的寄存器,而不能访问CPU总线上面的设备

7 32位处理器

32位微处理器:采用32位地址和数据总线。其地址空间达到了4G。

&emps;主流的32位嵌入式微处理器系列。

- ARM

- MIPS

- POWER PC

- X86

- SH系列

7.1 ARM处理器

ARM处理器。

- RISC体系结构

- 每条数据处理指令当中,都控制算术逻辑单元ALU和移位器

- 自动递增和自动寻址模式

- Load-Store体系结构。指令只能把内部寄存器和立即数作为操作数,只有加载/存储(Load-Store)指令才可以访问内存

- 所有指令都可以条件执行

ARM的数据类型。

- 字节(Byte):8bits

- 半字(Half-word):16bits(2Byte)

- 字(Word):32bits(4Byte)

ARM处理器有7中工作模式。

7.2 存储格式

7.2.1 大端格式

大端格式下的数据存放方式。

- 字数据的高字节存储在低地址。

- 字数据的低字节存放在高地址。

7.2.2 小端格式

小端格式下的数据存放方式。

- 字数据的低字节存储在高地址。

- 字数据的高字节存放在低地址。

7.3 I/O端口的编址方法

I/O端口的编址方法:I/O端口的地址安排方式。

- 存储器映射编址

- I/O映射编址

存储器映射编址方式和I/O映射编址方式比较。

| 存储器映射编址 | I/O映射方式 | |

|---|---|---|

| 优点 | 可采用丰富的内存操作指令访问I/O单元 无需单独的I/O地址译码电路 无需专用的I/O指令 |

|

| 缺点 | 外设占用内存空间 I/O程序不易读 |

I/O操作指令仅有单一的传送指令 I/O接口需有地址译码电路 |

| 举例 | ARM中,powerpc处理器,I/O端口与内存单元统一编址 | Intel 80X86系列 I/O端口与内存单元分开编址 I/O端口有自己独立的地址空间,其大小为64kB |

7.4 例题

- 在PowerPC处理器中,内存地址与I/O地址统一编址,访问内存单元和I/O设备是靠(B)来区分的。

A. 数据总线上输出的数据

B. 不同的地址

C. 内存与I/O设备使用不同的地址总线

D. 不同的指令

8 DSP处理器

8.1 简介

DSP:Digital Signal Processing,数字信号处理。

DSP处理器:专为数字信号处理而设计的处理器,快速实现各种数字信号处理算法。

- 多总线结构,允许CPU同时进行指令和数据的访问。因而,可实现流水线操作。

- 哈佛体系结构,程序和数据空间分开,可以同时访问指令和数据。

- 数字信号处理的运算特点:乘/加,及反复相乘求和(乘积累加)

- DSP设置了硬件乘法/累加器,能在单个指令周期内完成乘法/加法运算。

DSP主要应用:信号处理、图像处理、仪器、语音处理、控制、军事、通讯、医疗、家用电器等领域。

8.2 例题

- 以下针对嵌入式DSP处理器的描述,正确的是(A)

A. 一般采用哈佛结构

B. 单片机是嵌入式DSP处理器

C. 直接在片内固化嵌入式操作系统的代码模块

D. 使用VHDL语言进行内部程序设计

8.3 体系结构特点

双核处理器:基于单个半导体的一个处理器上拥有2个处理器核心。

- 由于将2个或多个运算核封装在一个芯片上,节省了大量晶体管、封装成本

- 显著提高处理器性能

- 兼容性好

- 系统升级方便

软件角度:2个或多个内核工作协调实现方式(多核处理器运行模式):

- 对称多处理技术(SMP):将2颗完全一样的处理器封装在一个芯片内,达到双倍或接近双倍的处理性能。节省运算资源。如Power 4。

- 非对称多处理技术(AMP):2个处理内核彼此不同,各自处理和执行特定的功能,在软件的协调下分担不同的计算任务。如OMAP5910。

8.4 体系结构特点

硬件角度:按计算内核的对等与否,多核处理器可分为同构多核和异构多核。

- 同构多核:计算内核相同,地位对等的称为同构多核。

- 异构多核:计算内核不相同,地位不对等的称为异构多核。多采用“主处理核+协处理器”的设计思路。

同构多核处理器。

- Intel酷睿架构处理器

- TI keystong架构。如TMS320C6678(简称C6678)是基于KeyStone架构的高性能多核DSP。

异构多核处理器。

- AMD核显

- TI OMAP/Davinci处理器系列,典型的包括OMAP3530、Davinci DM64xx系列等。

- Xilinx Zynq处理器,如Zynq-7000全可编程SoC系列。

8.5 例题

- 以下关于多核处理器的说法中,不正确的是(B)。

A. 采用多核处理器可以降低计算机系统的功耗和体积

B. SMP、BMP和MP是多核处理器系统通常采用的三种结构,采用哪种结构与应用场景相关,而无须考虑硬件的组成差异

C. 在多核处理器中,计算机可以同时执行多个进程,而操作系统中的多个线程也可以进行并行执行

D. 多核处理器是将两个或更多的独立处理器封装在一起,集成在一个电路中

- Flynn分类法根据计算机在执行程序的过程中(A)的不同组合,将计算机分为4类。当前主流的多核计算机属于(D)计算机。

(1)

A. 指令流和数据流

B. 数据流和控制流

C. 指令流和控制流

D. 数据流和总线带宽

(2)

A. SISD

B. SIMD

C. MISD

D. MIMD

- I/O口线:P0、P1、P2、P3

- 控制口线: $\overline{\text{PSEN}}$ 、ALE、 $\overline{\text{EA}}$ /VPP、RESET

- 电源:Vcc(+5v)、GND

- 时钟:XTAL1(片内震荡电路输入端)、XTAL2(片内振荡电路输出端)

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;

2.5 Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能 至少是不实际 |

目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

2.6 例题

- Flynn分类基于信息流特征将计算机分成4类,其中()只有理论意义而无实例(B)。

A. SISD

B. MISD

C. SIMD

D. MIMI

2.7 CISC与RISC

- 复杂指令集计算机(CISC)

- 精简指令集计算机(RISC)

- 尽管RISC体系与CISC体系相比较有较多的优点,但RISC和CISC各有优势。如超长指令集。

| 序号 | 类别 | CISC | RISC |

| 1 | 指令系统 | 指令数量很多 | 较少,通常少于100 |

| 2 | 执行时间 | 有些指令执行时间很长 | 没有较长执行时间的指令 |

| 3 | 编码长度 | 编码长度可变 | 编码长度固定 |

| 4 | 寻址方式 | 寻址方式多样 | 简单寻址 |

| 5 | 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器进行算术和逻辑操作 |

| 6 | 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术 |

- 超流水线

- 超标量

- 超长指令字

2.7.1 例题

- 嵌入式处理器指令系统一般采用精简指令集(RISC)或者复杂指令集(CISC),下列关于RISC和CISC描述错误的是(C)。

A. CISC的指令种类要多于RISC

B. RISC的寻址方式复杂,CISC的寻址方式简单

C. CISC的有些指令执行时间长,RISC多为单周期指令

D. RISC中的Load/Store指令对存储器进行操作

2.8 常用嵌入式微处理器介绍

- 8位微处理器

- 16位微处理器

- 32位微处理器

- 多核处理器

3 8位处理器

8位微处理器:是指使用8位数据总线的微处理器

- 8位处理器是指使用8位数据总线的微处理器,大部分8位微处理器有16位的地址总线。

- CISC,哈佛架构。

- 具有低成本、可靠性高、可扩充内存及接口设备等特点。

- 但功能、性能和片上资源相对16位/32位/64位嵌入式微控制器来讲也较简单。

常见型号包括

- Intel的MCS-51系列

- Fairchild及Mostek公司的3870系列

3.1 MCS-51

- I/O口线:P0、P1、P2、P3

- 控制口线: $\overline{\text{PSEN}}$ 、ALE、 $\overline{\text{EA}}$ /VPP、RESET

- 电源:Vcc(+5v)、GND

- 时钟:XTAL1(片内震荡电路输入端)、XTAL2(片内振荡电路输出端)

3.2 引脚说明

3.3 时钟电路

MCS-51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为垫片机产生时钟脉冲序列,振荡器的频率范围为1.2MHz~12MHz。

- 振荡周期:振荡一次所需时间。为单片机提供定时信号的振荡源的周期。

- 时钟周期:振荡脉冲二分频,又称为状态周期S。

- 机器周期:完成一个基本操作(如取指令、读存储器等)所需要的时间称为机器周期。机器周期由6个状态周期(12个振荡周期)组成。

- 指令周期:CPU执行一条指令所需要的时间可包含1~4个机器周期。

时钟电路方式。

- 内时钟方式:在XTAL1、XTAL2上外接定时元件,使其形成自激振荡器。定时元件采用由石英晶体和电容组成并联谐振电路。

- 外部时钟方式:XTAL2接地,XTAL1接外部振荡器。

4 中断系统

中断:CPU执行程序过程,随机接收到外设发来的中断请求,CPU可暂时中断当前正在执行的程序,转到相应的中断服务(子)程序进行处理(中断响应和中断服务)。处理完毕,再返回到原来的程序(被中断之处,即断点)(中断返回),继续运行下去,这个过程称作中断。

4.1 中断分类

请求CPU中断的设备或事件称为中断源,根据中断源的不同类别,可以把中断分为中断和内中断。

外中断:是指来自处理机和内存外部的中断,包括I/O设备发出的I/O中断、外部信号中断、各种定时器引起的时钟中断,以及程序调试中设置的断电等引起的调试中断等。外中断在狭义上一般被称为中断。

内中断:主要是指在处理机和内存内部产生的中断。内中断一般称为陷入或异常,包括程序运算引起的各种错误,如算术操作溢出、数据格式非法、除数为零等。

4.2 中断系统

中断识别:cpu响应中断后,只知道有中断请求但不知道是哪一个中断源,寻找中断源的操作过程称为中断识别。

中断识别的目的:形成该服务程序的入口地址。

| CPU识别中断的方法 | 说明 |

|---|---|

| 中断信号线法 | 每个中断源都有独立的中断请求信号线 |

| 中断软件查询法 | 中断服务程序轮询每个中断源 |

| 菊花链法 | 共享一根共同的中断请求线,中断确认信号以链式在各个模块间相连 |

| 总线仲裁法 | I/O设备在发中断请求前,先获得总线控制权,由总线仲裁机制来裁定谁可以发出中断请求信号 |

| 中断向量表法 | 根据中断号查找中断向量表来取得中断服务程序的入口地址 |

4.3 例题

- 计算机处理外部中断时,应该由操作系统保存的是(B)。

A. 程序计数器的内容

B. 通用寄存器的内容

C. 块表(TLB)的内容

D. Cache中的内容

5 16位处理器

16为微处理器:内部总线宽度为16位的微处理器。

- 比8位微处理器有较大的提高,数据宽度增加已被,实时处理能力更强,主频更高,集成度、RAM、ROM有较大的增加,更多的中断源,多路A/D转换通道等。

- MCS-96/196系列、MSP430系列、68H12系列。

MSP430系列单片机特点。

- 超低功耗

- 16位RISC CPU,冯诺依曼架构

- 高性能模拟技术以及丰富的片上外围模块

- 系统工作稳定

- 方便高效的开发环境

- 强大的处理能力

6 JTAG

JTAG的接口是一种特殊的4/5个管脚。

- TDI(测试数据输入)

- TDO(测试数据输出)

- TCK(测试时钟)

- TMS(测试模拟选择)

- TRST(测试复位)可选。

JTAG主要应用于:电路的边界扫描测试和编程芯片的在线系统编程、调试。

- 含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如Flash,RAM,Timers等。

6.1 例题

- JTAG是用来进行嵌入式处理器调试的标准化接口,下列描述中,正确的是(A)。

A. JTAG接口上一般包括模式选择、时钟、数据输入、数据输出、复位等信号

B. 当JTAG接口上面的时钟不正常时,也可以访问CPU内部的寄存器

C. JTAG只能用于调试,而不能用于进行芯片问题的检测

D. JTAG能够访问CPU内部的寄存器,而不能访问CPU总线上面的设备

7 32位处理器

32位微处理器:采用32位地址和数据总线。其地址空间达到了4G。

&emps;主流的32位嵌入式微处理器系列。

- ARM

- MIPS

- POWER PC

- X86

- SH系列

7.1 ARM处理器

ARM处理器。

- RISC体系结构

- 每条数据处理指令当中,都控制算术逻辑单元ALU和移位器

- 自动递增和自动寻址模式

- Load-Store体系结构。指令只能把内部寄存器和立即数作为操作数,只有加载/存储(Load-Store)指令才可以访问内存

- 所有指令都可以条件执行

ARM的数据类型。

- 字节(Byte):8bits

- 半字(Half-word):16bits(2Byte)

- 字(Word):32bits(4Byte)

ARM处理器有7中工作模式。

7.2 存储格式

7.2.1 大端格式

大端格式下的数据存放方式。

- 字数据的高字节存储在低地址。

- 字数据的低字节存放在高地址。

7.2.2 小端格式

小端格式下的数据存放方式。

- 字数据的低字节存储在高地址。

- 字数据的高字节存放在低地址。

7.3 I/O端口的编址方法

I/O端口的编址方法:I/O端口的地址安排方式。

- 存储器映射编址

- I/O映射编址

存储器映射编址方式和I/O映射编址方式比较。

| 存储器映射编址 | I/O映射方式 | |

|---|---|---|

| 优点 | 可采用丰富的内存操作指令访问I/O单元 无需单独的I/O地址译码电路 无需专用的I/O指令 |

|

| 缺点 | 外设占用内存空间 I/O程序不易读 |

I/O操作指令仅有单一的传送指令 I/O接口需有地址译码电路 |

| 举例 | ARM中,powerpc处理器,I/O端口与内存单元统一编址 | Intel 80X86系列 I/O端口与内存单元分开编址 I/O端口有自己独立的地址空间,其大小为64kB |

7.4 例题

- 在PowerPC处理器中,内存地址与I/O地址统一编址,访问内存单元和I/O设备是靠(B)来区分的。

A. 数据总线上输出的数据

B. 不同的地址

C. 内存与I/O设备使用不同的地址总线

D. 不同的指令

8 DSP处理器

8.1 简介

DSP:Digital Signal Processing,数字信号处理。

DSP处理器:专为数字信号处理而设计的处理器,快速实现各种数字信号处理算法。

- 多总线结构,允许CPU同时进行指令和数据的访问。因而,可实现流水线操作。

- 哈佛体系结构,程序和数据空间分开,可以同时访问指令和数据。

- 数字信号处理的运算特点:乘/加,及反复相乘求和(乘积累加)

- DSP设置了硬件乘法/累加器,能在单个指令周期内完成乘法/加法运算。

DSP主要应用:信号处理、图像处理、仪器、语音处理、控制、军事、通讯、医疗、家用电器等领域。

8.2 例题

- 以下针对嵌入式DSP处理器的描述,正确的是(A)

A. 一般采用哈佛结构

B. 单片机是嵌入式DSP处理器

C. 直接在片内固化嵌入式操作系统的代码模块

D. 使用VHDL语言进行内部程序设计

8.3 体系结构特点

双核处理器:基于单个半导体的一个处理器上拥有2个处理器核心。

- 由于将2个或多个运算核封装在一个芯片上,节省了大量晶体管、封装成本

- 显著提高处理器性能

- 兼容性好

- 系统升级方便

软件角度:2个或多个内核工作协调实现方式(多核处理器运行模式):

- 对称多处理技术(SMP):将2颗完全一样的处理器封装在一个芯片内,达到双倍或接近双倍的处理性能。节省运算资源。如Power 4。

- 非对称多处理技术(AMP):2个处理内核彼此不同,各自处理和执行特定的功能,在软件的协调下分担不同的计算任务。如OMAP5910。

8.4 体系结构特点

硬件角度:按计算内核的对等与否,多核处理器可分为同构多核和异构多核。

- 同构多核:计算内核相同,地位对等的称为同构多核。

- 异构多核:计算内核不相同,地位不对等的称为异构多核。多采用“主处理核+协处理器”的设计思路。

同构多核处理器。

- Intel酷睿架构处理器

- TI keystong架构。如TMS320C6678(简称C6678)是基于KeyStone架构的高性能多核DSP。

异构多核处理器。

- AMD核显

- TI OMAP/Davinci处理器系列,典型的包括OMAP3530、Davinci DM64xx系列等。

- Xilinx Zynq处理器,如Zynq-7000全可编程SoC系列。

8.5 例题

- 以下关于多核处理器的说法中,不正确的是(B)。

A. 采用多核处理器可以降低计算机系统的功耗和体积

B. SMP、BMP和MP是多核处理器系统通常采用的三种结构,采用哪种结构与应用场景相关,而无须考虑硬件的组成差异

C. 在多核处理器中,计算机可以同时执行多个进程,而操作系统中的多个线程也可以进行并行执行

D. 多核处理器是将两个或更多的独立处理器封装在一起,集成在一个电路中

- Flynn分类法根据计算机在执行程序的过程中(A)的不同组合,将计算机分为4类。当前主流的多核计算机属于(D)计算机。

(1)

A. 指令流和数据流

B. 数据流和控制流

C. 指令流和控制流

D. 数据流和总线带宽

(2)

A. SISD

B. SIMD

C. MISD

D. MIMD

3.2 引脚说明

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;

2.5 Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能 至少是不实际 |

目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

2.6 例题

- Flynn分类基于信息流特征将计算机分成4类,其中()只有理论意义而无实例(B)。

A. SISD

B. MISD

C. SIMD

D. MIMI

2.7 CISC与RISC

- 复杂指令集计算机(CISC)

- 精简指令集计算机(RISC)

- 尽管RISC体系与CISC体系相比较有较多的优点,但RISC和CISC各有优势。如超长指令集。

| 序号 | 类别 | CISC | RISC |

| 1 | 指令系统 | 指令数量很多 | 较少,通常少于100 |

| 2 | 执行时间 | 有些指令执行时间很长 | 没有较长执行时间的指令 |

| 3 | 编码长度 | 编码长度可变 | 编码长度固定 |

| 4 | 寻址方式 | 寻址方式多样 | 简单寻址 |

| 5 | 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器进行算术和逻辑操作 |

| 6 | 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术 |

- 超流水线

- 超标量

- 超长指令字

2.7.1 例题

- 嵌入式处理器指令系统一般采用精简指令集(RISC)或者复杂指令集(CISC),下列关于RISC和CISC描述错误的是(C)。

A. CISC的指令种类要多于RISC

B. RISC的寻址方式复杂,CISC的寻址方式简单

C. CISC的有些指令执行时间长,RISC多为单周期指令

D. RISC中的Load/Store指令对存储器进行操作

2.8 常用嵌入式微处理器介绍

- 8位微处理器

- 16位微处理器

- 32位微处理器

- 多核处理器

3 8位处理器

8位微处理器:是指使用8位数据总线的微处理器

- 8位处理器是指使用8位数据总线的微处理器,大部分8位微处理器有16位的地址总线。

- CISC,哈佛架构。

- 具有低成本、可靠性高、可扩充内存及接口设备等特点。

- 但功能、性能和片上资源相对16位/32位/64位嵌入式微控制器来讲也较简单。

常见型号包括

- Intel的MCS-51系列

- Fairchild及Mostek公司的3870系列

3.1 MCS-51

- I/O口线:P0、P1、P2、P3

- 控制口线: $\overline{\text{PSEN}}$ 、ALE、 $\overline{\text{EA}}$ /VPP、RESET

- 电源:Vcc(+5v)、GND

- 时钟:XTAL1(片内震荡电路输入端)、XTAL2(片内振荡电路输出端)

3.2 引脚说明

3.3 时钟电路

MCS-51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为垫片机产生时钟脉冲序列,振荡器的频率范围为1.2MHz~12MHz。

- 振荡周期:振荡一次所需时间。为单片机提供定时信号的振荡源的周期。

- 时钟周期:振荡脉冲二分频,又称为状态周期S。

- 机器周期:完成一个基本操作(如取指令、读存储器等)所需要的时间称为机器周期。机器周期由6个状态周期(12个振荡周期)组成。

- 指令周期:CPU执行一条指令所需要的时间可包含1~4个机器周期。

时钟电路方式。

- 内时钟方式:在XTAL1、XTAL2上外接定时元件,使其形成自激振荡器。定时元件采用由石英晶体和电容组成并联谐振电路。

- 外部时钟方式:XTAL2接地,XTAL1接外部振荡器。

4 中断系统

中断:CPU执行程序过程,随机接收到外设发来的中断请求,CPU可暂时中断当前正在执行的程序,转到相应的中断服务(子)程序进行处理(中断响应和中断服务)。处理完毕,再返回到原来的程序(被中断之处,即断点)(中断返回),继续运行下去,这个过程称作中断。

4.1 中断分类

请求CPU中断的设备或事件称为中断源,根据中断源的不同类别,可以把中断分为中断和内中断。

外中断:是指来自处理机和内存外部的中断,包括I/O设备发出的I/O中断、外部信号中断、各种定时器引起的时钟中断,以及程序调试中设置的断电等引起的调试中断等。外中断在狭义上一般被称为中断。

内中断:主要是指在处理机和内存内部产生的中断。内中断一般称为陷入或异常,包括程序运算引起的各种错误,如算术操作溢出、数据格式非法、除数为零等。

4.2 中断系统

中断识别:cpu响应中断后,只知道有中断请求但不知道是哪一个中断源,寻找中断源的操作过程称为中断识别。

中断识别的目的:形成该服务程序的入口地址。

| CPU识别中断的方法 | 说明 |

|---|---|

| 中断信号线法 | 每个中断源都有独立的中断请求信号线 |

| 中断软件查询法 | 中断服务程序轮询每个中断源 |

| 菊花链法 | 共享一根共同的中断请求线,中断确认信号以链式在各个模块间相连 |

| 总线仲裁法 | I/O设备在发中断请求前,先获得总线控制权,由总线仲裁机制来裁定谁可以发出中断请求信号 |

| 中断向量表法 | 根据中断号查找中断向量表来取得中断服务程序的入口地址 |

4.3 例题

- 计算机处理外部中断时,应该由操作系统保存的是(B)。

A. 程序计数器的内容

B. 通用寄存器的内容

C. 块表(TLB)的内容

D. Cache中的内容

5 16位处理器

16为微处理器:内部总线宽度为16位的微处理器。

- 比8位微处理器有较大的提高,数据宽度增加已被,实时处理能力更强,主频更高,集成度、RAM、ROM有较大的增加,更多的中断源,多路A/D转换通道等。

- MCS-96/196系列、MSP430系列、68H12系列。

MSP430系列单片机特点。

- 超低功耗

- 16位RISC CPU,冯诺依曼架构

- 高性能模拟技术以及丰富的片上外围模块

- 系统工作稳定

- 方便高效的开发环境

- 强大的处理能力

6 JTAG

JTAG的接口是一种特殊的4/5个管脚。

- TDI(测试数据输入)

- TDO(测试数据输出)

- TCK(测试时钟)

- TMS(测试模拟选择)

- TRST(测试复位)可选。

JTAG主要应用于:电路的边界扫描测试和编程芯片的在线系统编程、调试。

- 含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如Flash,RAM,Timers等。

6.1 例题

- JTAG是用来进行嵌入式处理器调试的标准化接口,下列描述中,正确的是(A)。

A. JTAG接口上一般包括模式选择、时钟、数据输入、数据输出、复位等信号

B. 当JTAG接口上面的时钟不正常时,也可以访问CPU内部的寄存器

C. JTAG只能用于调试,而不能用于进行芯片问题的检测

D. JTAG能够访问CPU内部的寄存器,而不能访问CPU总线上面的设备

7 32位处理器

32位微处理器:采用32位地址和数据总线。其地址空间达到了4G。

&emps;主流的32位嵌入式微处理器系列。

- ARM

- MIPS

- POWER PC

- X86

- SH系列

7.1 ARM处理器

ARM处理器。

- RISC体系结构

- 每条数据处理指令当中,都控制算术逻辑单元ALU和移位器

- 自动递增和自动寻址模式

- Load-Store体系结构。指令只能把内部寄存器和立即数作为操作数,只有加载/存储(Load-Store)指令才可以访问内存

- 所有指令都可以条件执行

ARM的数据类型。

- 字节(Byte):8bits

- 半字(Half-word):16bits(2Byte)

- 字(Word):32bits(4Byte)

ARM处理器有7中工作模式。

7.2 存储格式

7.2.1 大端格式

大端格式下的数据存放方式。

- 字数据的高字节存储在低地址。

- 字数据的低字节存放在高地址。

7.2.2 小端格式

小端格式下的数据存放方式。

- 字数据的低字节存储在高地址。

- 字数据的高字节存放在低地址。

7.3 I/O端口的编址方法

I/O端口的编址方法:I/O端口的地址安排方式。

- 存储器映射编址

- I/O映射编址

存储器映射编址方式和I/O映射编址方式比较。

| 存储器映射编址 | I/O映射方式 | |

|---|---|---|

| 优点 | 可采用丰富的内存操作指令访问I/O单元 无需单独的I/O地址译码电路 无需专用的I/O指令 |

|

| 缺点 | 外设占用内存空间 I/O程序不易读 |

I/O操作指令仅有单一的传送指令 I/O接口需有地址译码电路 |

| 举例 | ARM中,powerpc处理器,I/O端口与内存单元统一编址 | Intel 80X86系列 I/O端口与内存单元分开编址 I/O端口有自己独立的地址空间,其大小为64kB |

7.4 例题

- 在PowerPC处理器中,内存地址与I/O地址统一编址,访问内存单元和I/O设备是靠(B)来区分的。

A. 数据总线上输出的数据

B. 不同的地址

C. 内存与I/O设备使用不同的地址总线

D. 不同的指令

8 DSP处理器

8.1 简介

DSP:Digital Signal Processing,数字信号处理。

DSP处理器:专为数字信号处理而设计的处理器,快速实现各种数字信号处理算法。

- 多总线结构,允许CPU同时进行指令和数据的访问。因而,可实现流水线操作。

- 哈佛体系结构,程序和数据空间分开,可以同时访问指令和数据。

- 数字信号处理的运算特点:乘/加,及反复相乘求和(乘积累加)

- DSP设置了硬件乘法/累加器,能在单个指令周期内完成乘法/加法运算。

DSP主要应用:信号处理、图像处理、仪器、语音处理、控制、军事、通讯、医疗、家用电器等领域。

8.2 例题

- 以下针对嵌入式DSP处理器的描述,正确的是(A)

A. 一般采用哈佛结构

B. 单片机是嵌入式DSP处理器

C. 直接在片内固化嵌入式操作系统的代码模块

D. 使用VHDL语言进行内部程序设计

8.3 体系结构特点

双核处理器:基于单个半导体的一个处理器上拥有2个处理器核心。

- 由于将2个或多个运算核封装在一个芯片上,节省了大量晶体管、封装成本

- 显著提高处理器性能

- 兼容性好

- 系统升级方便

软件角度:2个或多个内核工作协调实现方式(多核处理器运行模式):

- 对称多处理技术(SMP):将2颗完全一样的处理器封装在一个芯片内,达到双倍或接近双倍的处理性能。节省运算资源。如Power 4。

- 非对称多处理技术(AMP):2个处理内核彼此不同,各自处理和执行特定的功能,在软件的协调下分担不同的计算任务。如OMAP5910。

8.4 体系结构特点

硬件角度:按计算内核的对等与否,多核处理器可分为同构多核和异构多核。

- 同构多核:计算内核相同,地位对等的称为同构多核。

- 异构多核:计算内核不相同,地位不对等的称为异构多核。多采用“主处理核+协处理器”的设计思路。

同构多核处理器。

- Intel酷睿架构处理器

- TI keystong架构。如TMS320C6678(简称C6678)是基于KeyStone架构的高性能多核DSP。

异构多核处理器。

- AMD核显

- TI OMAP/Davinci处理器系列,典型的包括OMAP3530、Davinci DM64xx系列等。

- Xilinx Zynq处理器,如Zynq-7000全可编程SoC系列。

8.5 例题

- 以下关于多核处理器的说法中,不正确的是(B)。

A. 采用多核处理器可以降低计算机系统的功耗和体积

B. SMP、BMP和MP是多核处理器系统通常采用的三种结构,采用哪种结构与应用场景相关,而无须考虑硬件的组成差异

C. 在多核处理器中,计算机可以同时执行多个进程,而操作系统中的多个线程也可以进行并行执行

D. 多核处理器是将两个或更多的独立处理器封装在一起,集成在一个电路中

- Flynn分类法根据计算机在执行程序的过程中(A)的不同组合,将计算机分为4类。当前主流的多核计算机属于(D)计算机。

(1)

A. 指令流和数据流

B. 数据流和控制流

C. 指令流和控制流

D. 数据流和总线带宽

(2)

A. SISD

B. SIMD

C. MISD

D. MIMD

3.3 时钟电路

MCS-51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为垫片机产生时钟脉冲序列,振荡器的频率范围为1.2MHz~12MHz。

- 振荡周期:振荡一次所需时间。为单片机提供定时信号的振荡源的周期。

- 时钟周期:振荡脉冲二分频,又称为状态周期S。

- 机器周期:完成一个基本操作(如取指令、读存储器等)所需要的时间称为机器周期。机器周期由6个状态周期(12个振荡周期)组成。

- 指令周期:CPU执行一条指令所需要的时间可包含1~4个机器周期。

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;

2.5 Flynn分类法

| 体系结构类型 | 结构 | 关键特性 | 代表 |

|---|---|---|---|

| 单指令流单数据流SISD | 控制部分:一个 处理器:一个 主存模块:一个 |

单处理器系统 | |

| 单指令流多数据流SIMD | 控制部分:一个 处理器:多个 主存模块:多个 |

各处理器以异步的形式执行同一条指令 | 并行处理机 阵列处理机 超级向量处理机 |

| 多指令流单数据流MISD | 控制部分:多个 处理器:一个 主存模块:多个 |

被证明不可能 至少是不实际 |

目前没有,有文献称流水线计算机为此类 |

| 多指令流多数据流MIMD | 控制部分:多个 处理器:多个 主存模块:多个 |

能够实现作业、任务、指令等各级全面并行 | 多处理机系统 多计算机 |

2.6 例题

- Flynn分类基于信息流特征将计算机分成4类,其中()只有理论意义而无实例(B)。

A. SISD

B. MISD

C. SIMD

D. MIMI

2.7 CISC与RISC

- 复杂指令集计算机(CISC)

- 精简指令集计算机(RISC)

- 尽管RISC体系与CISC体系相比较有较多的优点,但RISC和CISC各有优势。如超长指令集。

| 序号 | 类别 | CISC | RISC |

| 1 | 指令系统 | 指令数量很多 | 较少,通常少于100 |

| 2 | 执行时间 | 有些指令执行时间很长 | 没有较长执行时间的指令 |

| 3 | 编码长度 | 编码长度可变 | 编码长度固定 |

| 4 | 寻址方式 | 寻址方式多样 | 简单寻址 |

| 5 | 操作 | 可以对存储器和寄存器进行算术和逻辑操作 | 只能对寄存器进行算术和逻辑操作 |

| 6 | 编译 | 难以用优化编译器生成高效的目标代码程序 | 采用优化编译技术 |

- 超流水线

- 超标量

- 超长指令字

2.7.1 例题

- 嵌入式处理器指令系统一般采用精简指令集(RISC)或者复杂指令集(CISC),下列关于RISC和CISC描述错误的是(C)。

A. CISC的指令种类要多于RISC

B. RISC的寻址方式复杂,CISC的寻址方式简单

C. CISC的有些指令执行时间长,RISC多为单周期指令

D. RISC中的Load/Store指令对存储器进行操作

2.8 常用嵌入式微处理器介绍

- 8位微处理器

- 16位微处理器

- 32位微处理器

- 多核处理器

3 8位处理器

8位微处理器:是指使用8位数据总线的微处理器

- 8位处理器是指使用8位数据总线的微处理器,大部分8位微处理器有16位的地址总线。

- CISC,哈佛架构。

- 具有低成本、可靠性高、可扩充内存及接口设备等特点。

- 但功能、性能和片上资源相对16位/32位/64位嵌入式微控制器来讲也较简单。

常见型号包括

- Intel的MCS-51系列

- Fairchild及Mostek公司的3870系列

3.1 MCS-51

- I/O口线:P0、P1、P2、P3

- 控制口线: $\overline{\text{PSEN}}$ 、ALE、 $\overline{\text{EA}}$ /VPP、RESET

- 电源:Vcc(+5v)、GND

- 时钟:XTAL1(片内震荡电路输入端)、XTAL2(片内振荡电路输出端)

3.2 引脚说明

3.3 时钟电路

MCS-51芯片内部有时钟电路,但晶体振荡器和微调电容必须外接。时钟电路为垫片机产生时钟脉冲序列,振荡器的频率范围为1.2MHz~12MHz。

- 振荡周期:振荡一次所需时间。为单片机提供定时信号的振荡源的周期。

- 时钟周期:振荡脉冲二分频,又称为状态周期S。

- 机器周期:完成一个基本操作(如取指令、读存储器等)所需要的时间称为机器周期。机器周期由6个状态周期(12个振荡周期)组成。

- 指令周期:CPU执行一条指令所需要的时间可包含1~4个机器周期。

时钟电路方式。

- 内时钟方式:在XTAL1、XTAL2上外接定时元件,使其形成自激振荡器。定时元件采用由石英晶体和电容组成并联谐振电路。

- 外部时钟方式:XTAL2接地,XTAL1接外部振荡器。

4 中断系统

中断:CPU执行程序过程,随机接收到外设发来的中断请求,CPU可暂时中断当前正在执行的程序,转到相应的中断服务(子)程序进行处理(中断响应和中断服务)。处理完毕,再返回到原来的程序(被中断之处,即断点)(中断返回),继续运行下去,这个过程称作中断。

4.1 中断分类

请求CPU中断的设备或事件称为中断源,根据中断源的不同类别,可以把中断分为中断和内中断。

外中断:是指来自处理机和内存外部的中断,包括I/O设备发出的I/O中断、外部信号中断、各种定时器引起的时钟中断,以及程序调试中设置的断电等引起的调试中断等。外中断在狭义上一般被称为中断。

内中断:主要是指在处理机和内存内部产生的中断。内中断一般称为陷入或异常,包括程序运算引起的各种错误,如算术操作溢出、数据格式非法、除数为零等。

4.2 中断系统

中断识别:cpu响应中断后,只知道有中断请求但不知道是哪一个中断源,寻找中断源的操作过程称为中断识别。

中断识别的目的:形成该服务程序的入口地址。

| CPU识别中断的方法 | 说明 |

|---|---|

| 中断信号线法 | 每个中断源都有独立的中断请求信号线 |

| 中断软件查询法 | 中断服务程序轮询每个中断源 |

| 菊花链法 | 共享一根共同的中断请求线,中断确认信号以链式在各个模块间相连 |

| 总线仲裁法 | I/O设备在发中断请求前,先获得总线控制权,由总线仲裁机制来裁定谁可以发出中断请求信号 |

| 中断向量表法 | 根据中断号查找中断向量表来取得中断服务程序的入口地址 |

4.3 例题

- 计算机处理外部中断时,应该由操作系统保存的是(B)。

A. 程序计数器的内容

B. 通用寄存器的内容

C. 块表(TLB)的内容

D. Cache中的内容

5 16位处理器

16为微处理器:内部总线宽度为16位的微处理器。

- 比8位微处理器有较大的提高,数据宽度增加已被,实时处理能力更强,主频更高,集成度、RAM、ROM有较大的增加,更多的中断源,多路A/D转换通道等。

- MCS-96/196系列、MSP430系列、68H12系列。

MSP430系列单片机特点。

- 超低功耗

- 16位RISC CPU,冯诺依曼架构

- 高性能模拟技术以及丰富的片上外围模块

- 系统工作稳定

- 方便高效的开发环境

- 强大的处理能力

6 JTAG

JTAG的接口是一种特殊的4/5个管脚。

- TDI(测试数据输入)

- TDO(测试数据输出)

- TCK(测试时钟)

- TMS(测试模拟选择)

- TRST(测试复位)可选。

JTAG主要应用于:电路的边界扫描测试和编程芯片的在线系统编程、调试。

- 含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如Flash,RAM,Timers等。

6.1 例题

- JTAG是用来进行嵌入式处理器调试的标准化接口,下列描述中,正确的是(A)。

A. JTAG接口上一般包括模式选择、时钟、数据输入、数据输出、复位等信号

B. 当JTAG接口上面的时钟不正常时,也可以访问CPU内部的寄存器

C. JTAG只能用于调试,而不能用于进行芯片问题的检测

D. JTAG能够访问CPU内部的寄存器,而不能访问CPU总线上面的设备

7 32位处理器

32位微处理器:采用32位地址和数据总线。其地址空间达到了4G。

&emps;主流的32位嵌入式微处理器系列。

- ARM

- MIPS

- POWER PC

- X86

- SH系列

7.1 ARM处理器

ARM处理器。

- RISC体系结构

- 每条数据处理指令当中,都控制算术逻辑单元ALU和移位器

- 自动递增和自动寻址模式

- Load-Store体系结构。指令只能把内部寄存器和立即数作为操作数,只有加载/存储(Load-Store)指令才可以访问内存

- 所有指令都可以条件执行

ARM的数据类型。

- 字节(Byte):8bits

- 半字(Half-word):16bits(2Byte)

- 字(Word):32bits(4Byte)

ARM处理器有7中工作模式。

7.2 存储格式

7.2.1 大端格式

大端格式下的数据存放方式。

- 字数据的高字节存储在低地址。

- 字数据的低字节存放在高地址。

7.2.2 小端格式

小端格式下的数据存放方式。

- 字数据的低字节存储在高地址。

- 字数据的高字节存放在低地址。

7.3 I/O端口的编址方法

I/O端口的编址方法:I/O端口的地址安排方式。

- 存储器映射编址

- I/O映射编址

存储器映射编址方式和I/O映射编址方式比较。

| 存储器映射编址 | I/O映射方式 | |

|---|---|---|

| 优点 | 可采用丰富的内存操作指令访问I/O单元 无需单独的I/O地址译码电路 无需专用的I/O指令 |

|

| 缺点 | 外设占用内存空间 I/O程序不易读 |

I/O操作指令仅有单一的传送指令 I/O接口需有地址译码电路 |

| 举例 | ARM中,powerpc处理器,I/O端口与内存单元统一编址 | Intel 80X86系列 I/O端口与内存单元分开编址 I/O端口有自己独立的地址空间,其大小为64kB |

7.4 例题

- 在PowerPC处理器中,内存地址与I/O地址统一编址,访问内存单元和I/O设备是靠(B)来区分的。

A. 数据总线上输出的数据

B. 不同的地址

C. 内存与I/O设备使用不同的地址总线

D. 不同的指令

8 DSP处理器

8.1 简介

DSP:Digital Signal Processing,数字信号处理。

DSP处理器:专为数字信号处理而设计的处理器,快速实现各种数字信号处理算法。

- 多总线结构,允许CPU同时进行指令和数据的访问。因而,可实现流水线操作。

- 哈佛体系结构,程序和数据空间分开,可以同时访问指令和数据。

- 数字信号处理的运算特点:乘/加,及反复相乘求和(乘积累加)

- DSP设置了硬件乘法/累加器,能在单个指令周期内完成乘法/加法运算。

DSP主要应用:信号处理、图像处理、仪器、语音处理、控制、军事、通讯、医疗、家用电器等领域。

8.2 例题

- 以下针对嵌入式DSP处理器的描述,正确的是(A)

A. 一般采用哈佛结构

B. 单片机是嵌入式DSP处理器

C. 直接在片内固化嵌入式操作系统的代码模块

D. 使用VHDL语言进行内部程序设计

8.3 体系结构特点

双核处理器:基于单个半导体的一个处理器上拥有2个处理器核心。

- 由于将2个或多个运算核封装在一个芯片上,节省了大量晶体管、封装成本

- 显著提高处理器性能

- 兼容性好

- 系统升级方便

软件角度:2个或多个内核工作协调实现方式(多核处理器运行模式):

- 对称多处理技术(SMP):将2颗完全一样的处理器封装在一个芯片内,达到双倍或接近双倍的处理性能。节省运算资源。如Power 4。

- 非对称多处理技术(AMP):2个处理内核彼此不同,各自处理和执行特定的功能,在软件的协调下分担不同的计算任务。如OMAP5910。

8.4 体系结构特点

硬件角度:按计算内核的对等与否,多核处理器可分为同构多核和异构多核。

- 同构多核:计算内核相同,地位对等的称为同构多核。

- 异构多核:计算内核不相同,地位不对等的称为异构多核。多采用“主处理核+协处理器”的设计思路。

同构多核处理器。

- Intel酷睿架构处理器

- TI keystong架构。如TMS320C6678(简称C6678)是基于KeyStone架构的高性能多核DSP。

异构多核处理器。

- AMD核显

- TI OMAP/Davinci处理器系列,典型的包括OMAP3530、Davinci DM64xx系列等。

- Xilinx Zynq处理器,如Zynq-7000全可编程SoC系列。

8.5 例题

- 以下关于多核处理器的说法中,不正确的是(B)。

A. 采用多核处理器可以降低计算机系统的功耗和体积

B. SMP、BMP和MP是多核处理器系统通常采用的三种结构,采用哪种结构与应用场景相关,而无须考虑硬件的组成差异

C. 在多核处理器中,计算机可以同时执行多个进程,而操作系统中的多个线程也可以进行并行执行

D. 多核处理器是将两个或更多的独立处理器封装在一起,集成在一个电路中

- Flynn分类法根据计算机在执行程序的过程中(A)的不同组合,将计算机分为4类。当前主流的多核计算机属于(D)计算机。

(1)

A. 指令流和数据流

B. 数据流和控制流

C. 指令流和控制流

D. 数据流和总线带宽

(2)

A. SISD

B. SIMD

C. MISD

D. MIMD

时钟电路方式。

- 内时钟方式:在XTAL1、XTAL2上外接定时元件,使其形成自激振荡器。定时元件采用由石英晶体和电容组成并联谐振电路。

第十一章——嵌入式微处理器基础

前言:

计算机第十一章节主要知识点。

1 知识点介绍

- 嵌入式微处理器的结构与类型

- 嵌入式微处理器的体系结构

- 常用嵌入式微处理器介绍

2 嵌入式微处理器的结构和类型

- 嵌入式微处理器的基本结构

- 嵌入式微处理器的分类

嵌入式硬件系统一般由嵌入式微处理器、存储器和输入/输出部分组成。

嵌入式微处理器是嵌入式硬件系统的核心,通常由以下3大部分组成。

- 控制单元:主要负责取指、译码和取数等基本操作并发送主要的控制指令。包括两个重要的寄存器:程序计数器(PC)、指令寄存器。

- 算术逻辑单元:主要处理数值型数据和进行逻辑运算工作。

- 寄存器:暂存临时性的数据。

2.1 MCU/EMPU

&emps;嵌入式微控制器(MCU:Micro Controller Unit):又称为单片机,片上外设资源一般比较丰富,适用于控制。

- MCU集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串口、PWM、A/D、D/A、Flash、EEPROM等。

- 最大的特点是单片化,体积小,功耗和成本低,可靠性高。

- 8051、MCS-251

- 目前约占70%的时长份额

嵌入式微处理器(EMPU:Embedded Micro Processing Unit):又称为单板机,由通用计算机中的CPU发展而来,仅保留和嵌入式应用紧密相关的功能硬件。

- 特征:具有32位及以上的处理器,具有较高的性能。

- 通常嵌入式微处理器把CPU、ROM、RAM及I/O等模块做到同一个芯片上。

- ARM、MIPS、POWER PC等。

2.2 DSP/SOC

&emps;嵌入式DSP处理器(DSP:Digital Signal Processor):专门用于信号处理方面的处理器。

- 在系统结构和指令算法方面进行了特殊设计,具有很高的编译效果和指令执行速度,其处理速度笔最快的CPU还快10~50倍。

- 哈佛结构,流水线操作。

- 在数字滤波、FFT、频谱分析等方面获得了大量的应用。

嵌入式片上系统(SOC):追求产品系统最大包容的集成器件。

- 最大的特点:成功实现了软硬件的无缝结合,直接在微处理器片内嵌入操作系统的代码模块。

- 减少了系统的体积和功耗、提高了可靠性和设计产生效率。

片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核。

2.3 嵌入式微处理器的应用

2.3.1 例题

- 嵌入式处理器是嵌入式系统的核心,一般可分为嵌入式微处理器(MPU),微控制器(MCU),数字信号处理器(DSP)和片上系统(SOC)。以下描述中不正确的是(A)。

A. MPU在可靠性等方面做了各种增强,适用于运算量较大的只能系统设计

B. 微控制器俗称单片机,其品种数量非常丰富

C. DSP处理器对系统结构和指令进行了特殊设计,适合数字信号处理

D. 片上系统设计的关键是IP核,IP核一般分为硬核、软核和固核

2.4 体系结构

- 冯诺依曼与哈佛体系结构

- Flynn分类法

- CISC与RISC

2.4.1 冯诺依曼体系结构

冯诺依曼体系结构:也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构

- 程序计数器(PC)是CPU内部指示指令和数据存储位置的寄存器。

- CPU通过程序计数器提供的地址信息,对存储器进行寻址,找到需要的指令或数据,然后对指令进行译码,最后执行指令规定的操作。

&emps;特点。

- 采用单一的地址及数据总线,程序指令和数据的宽度相同。

- 处理器执行指令时,先从存储器中取出指令解码,再取操作数执行计算,即使单挑指令也要耗费几个甚至几十个周期。

- 程序计数器只负责提供程序执行所需的指令和数据,而不决定程序流程。

使用冯诺依曼结构的处理器。

- 英特尔公司的8086及其他CPU

- ARM公司的额ARM7

- MIPS公司的MIPS处理器

2.4.2 哈佛体系结构

哈佛体系结构:是一种将程序指令存储和数据存储分开的存储器结构。

特点。

- 程序存储器和数据存储器采用不同的总线,提供较大的存储器贷款;

- 较高的数字信号处理器性能;

- 允许在一个机器周期内同时获取指令字和操作数,提高执行速度,取指令和执行能完全重叠;

使用哈佛结构的处理器。

- DSP处理器;

- 摩托罗拉公司的MC68系列;

- Zilog公司的Z8系列;

- ATMEL公司的AVR系列;

- ARM公司的ARM9、ARM10和ARM11等;